Read-back self-reconfiguration-based fault-tolerant method for SoPC (Programming System on Chip) chip

A self-reconfiguration, chip technology, applied in the direction of responding to errors, etc., can solve problems such as failure to repair, small size, complex and unknown failure processing, lack of effective methods, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

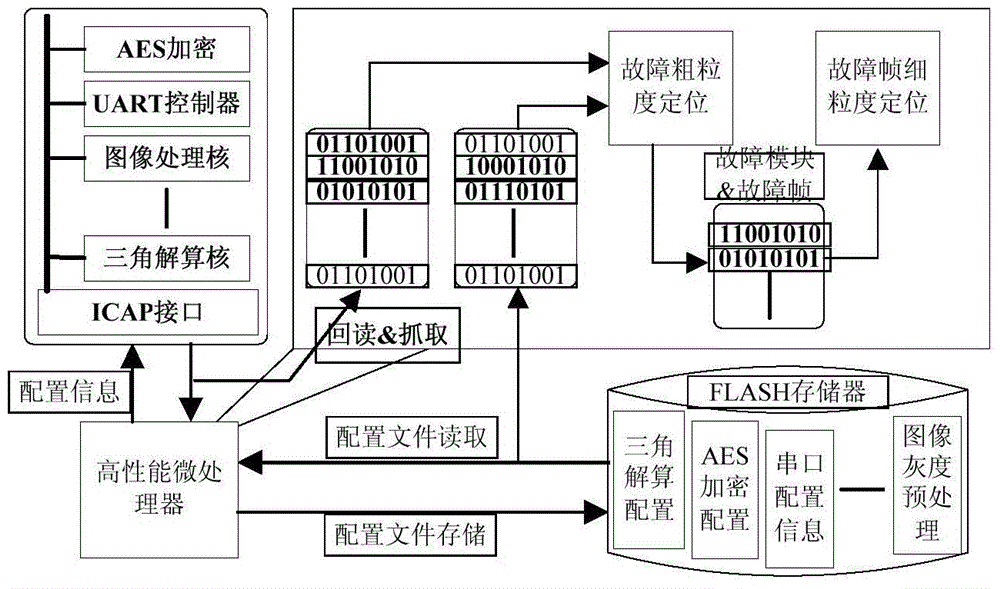

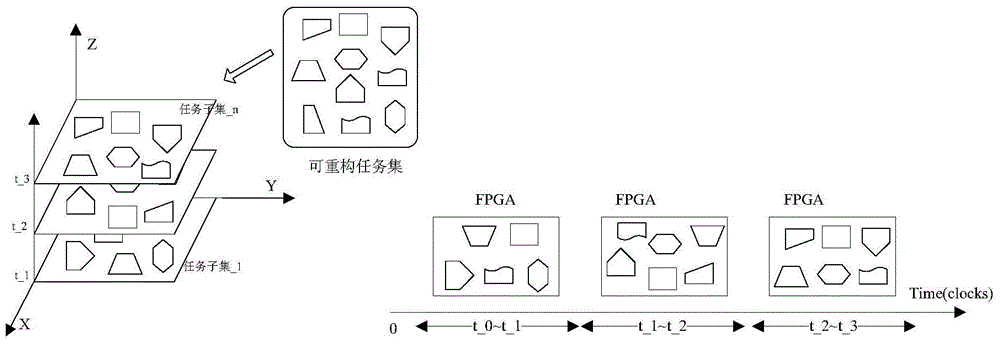

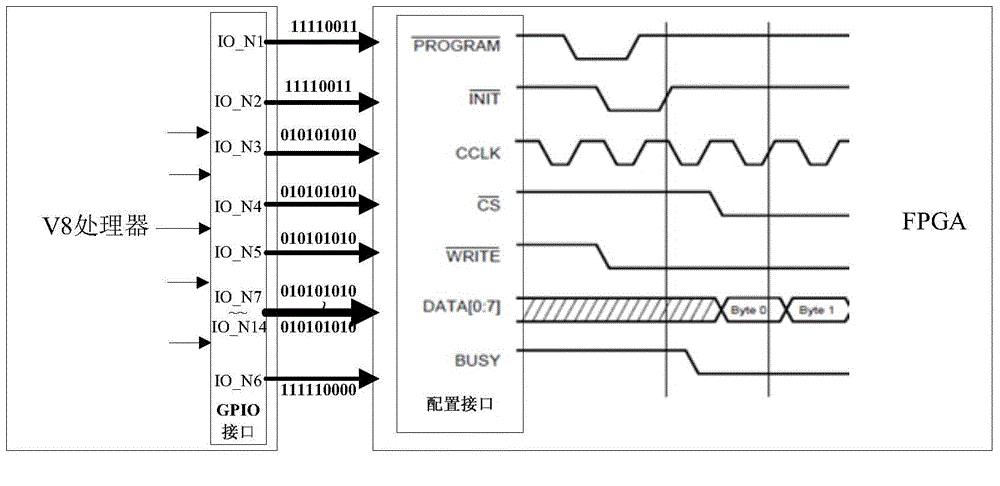

[0038] The present invention studies the autonomous fault-tolerant design of the domestic SoPC chip BM3109, and seeks to realize autonomous fault detection and fault repair of the chip based on the "readback-reconfiguration" method without increasing the area of the SoPC chip. By breaking through this key technology, it will help improve the reliability of SoPC chips in the application of outer space environments, and help promote the development of domestic SoPC chips. The invention provides an autonomous fault tolerance and fault recovery capability for the domestic SoPC chip BM3109, without adding peripheral detection equipment and detection circuits, based on the fault tolerance mechanism of "readback-self-reconfiguration", the BM3109 can operate in the space environment Under this condition, the fault detection, fault interpretation, and fault repair can be completed independently.

[0039] Fault detection: Start to configure the control pin of Flash in BM3109, under th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More