Array substrate, manufacturing method of array substrate and display device

A technology of an array substrate and a manufacturing method, which is applied in the display field, can solve the problems of increased charge asymmetry, increased signal delay and afterimage, large leakage current, etc., and achieves the effects of reducing power consumption, reducing parasitic capacitance, and reducing overlapping capacitance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] Specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings. It should be understood that the specific embodiments described here are only used to illustrate and explain the present invention, and are not intended to limit the present invention.

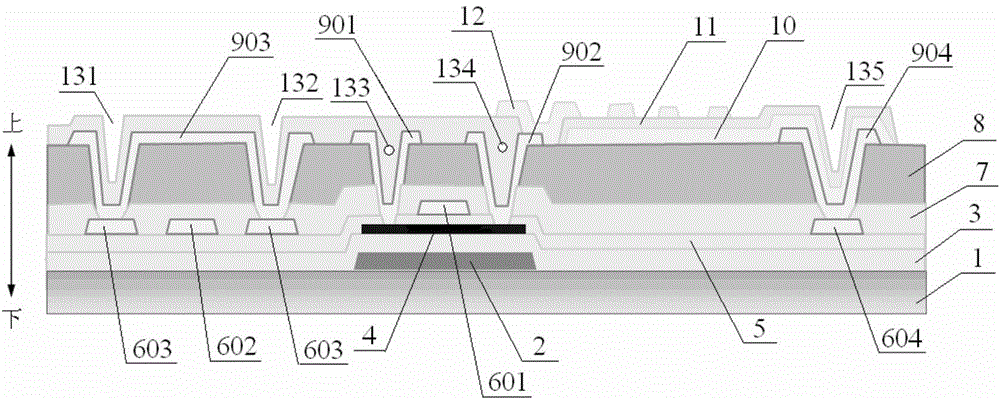

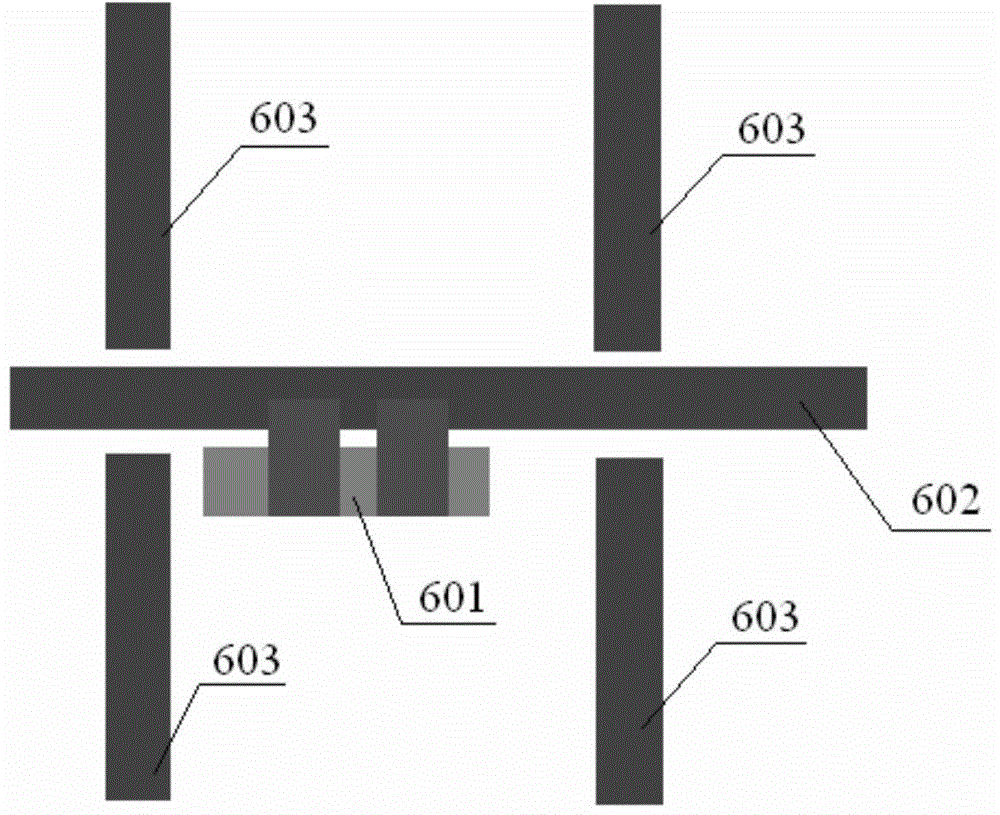

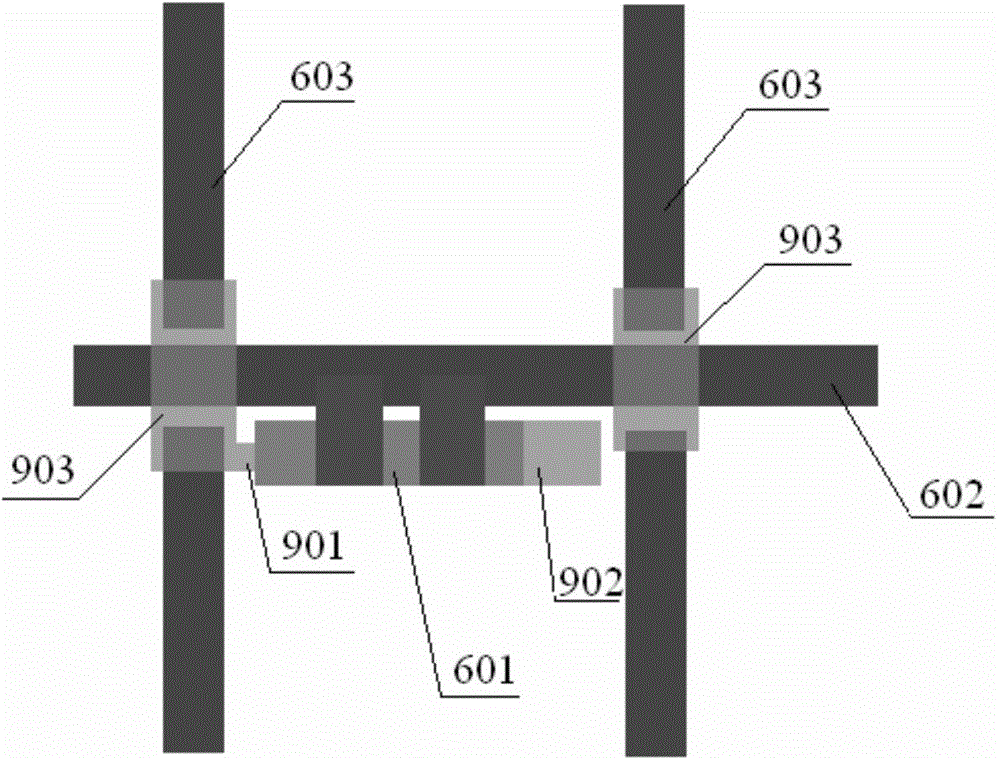

[0043] The present invention firstly provides an array substrate, such as Figure 1-Figure 3 As shown, the array substrate includes a first pattern layer and a second pattern layer sequentially arranged above the base substrate 1 , and an organic insulating layer is arranged between the first pattern layer and the second pattern layer. Wherein, the first pattern layer (refer to figure 2 ) includes a gate 601 of the thin film transistor, a gate line 602, and a data line 603, the gate 601 is connected to the gate line 602, the data line 603 is disconnected by the gate line 602, and the data line 603 is insulated from the gate line 602. The second pattern layer ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More