Accelerating simulated annealing method for integrated circuit layout

A technology of simulated annealing and integrated circuits, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve the problems of reducing layout time and unacceptable algorithm running time, so as to reduce layout time and reduce algorithm running time, reducing the effect of invalid moves

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

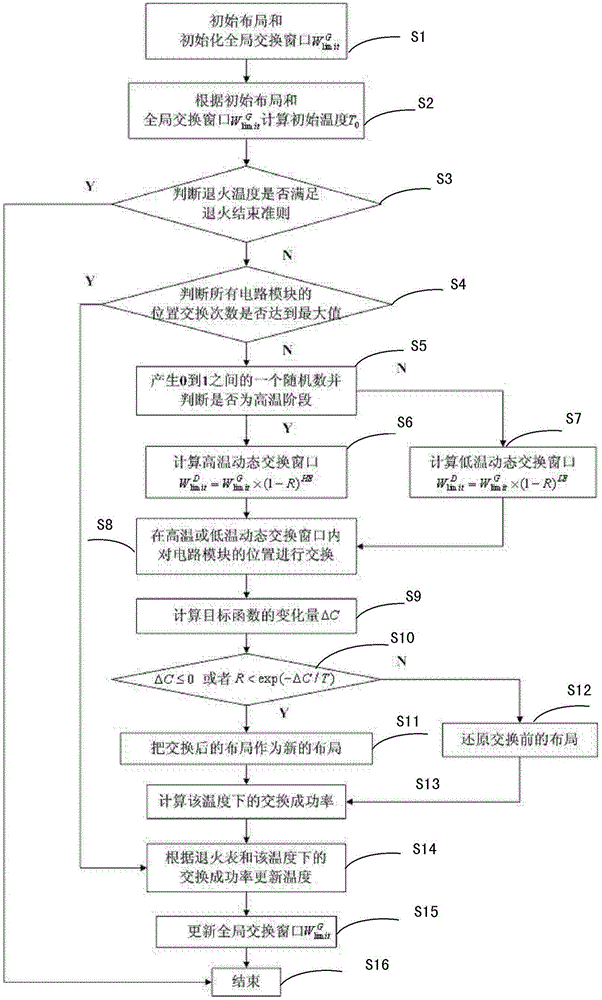

[0018] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

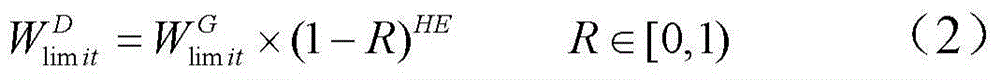

[0019] An accelerated simulated annealing (SA) method for integrated circuit layout of the present invention changes the calculation method of the exchange window in the simulated annealing method, so that the exchange window is not only determined by the exchange success rate at the previous temperature, but also related to It is related to a random number R that determines whether a certain exchange is accepted, so that the window size of each exchange changes dynamically with the random number R. In addition, different dynamic exchange window adjustment strategies are adopted for the high-temperature and low-temperature stages of annealing, that is, the dynamic exchange window is narrowed in the high-temperature stage; ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More