System and method for accelerating chip interrupt controller verification

A technology for accelerating chips and controllers, which is applied in the verification field of accelerating chip interrupt controllers, can solve problems such as difficulty in occurrence, harsh interrupt trigger conditions, and cost, and achieve the effects of highlighting substantive features, making significant progress, and shortening simulation time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] In order to clearly illustrate the technical features of the solution, the solution will be described below through a specific implementation mode combined with the accompanying drawings.

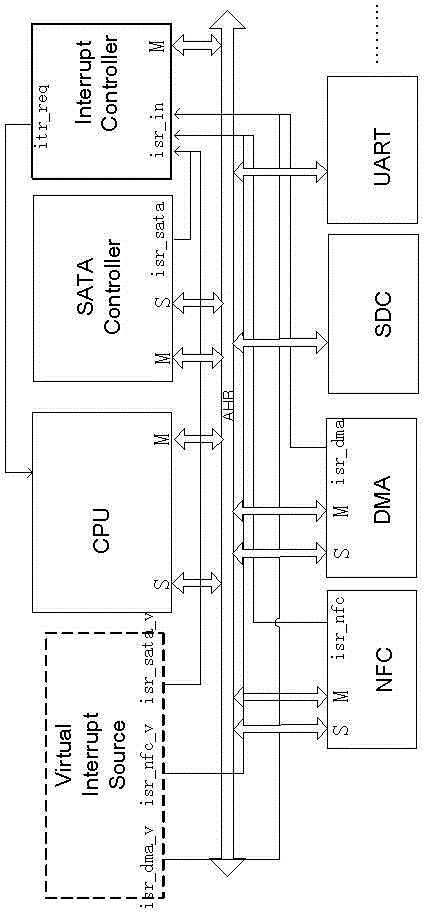

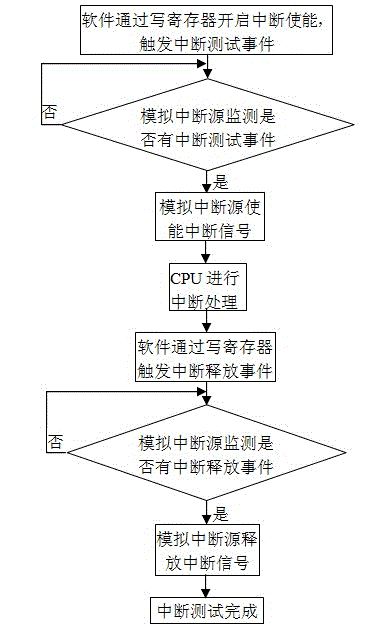

[0022] The acceleration chip interrupt controller verification system of this solution, the interrupt trigger module writes a specific register value into the reserved register through the software interface to trigger the interrupt test event; the interrupt release module writes a specific register value into the reserved register through the software interface Write a specific register value to trigger the interrupt release event; simulate the interrupt source module (Virtual Interrupt Source), monitor the interrupt test event and the interrupt release event in real time, and turn all the actual interrupt signals in turn after the interrupt test event is detected. Trigger, and release each interrupt signal after detecting the interrupt release event.

[0023] When the software star...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More