Method and system for configuring PCIE bus interface in self-adaption mode

A bus interface, self-adaptive technology, applied in the field of self-adaptive configuration PCIE bus interface, can solve problems such as low efficiency, achieve high efficiency, improve flexibility and compatibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] In order to make the object, technical solution and advantages of the present invention more clear, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

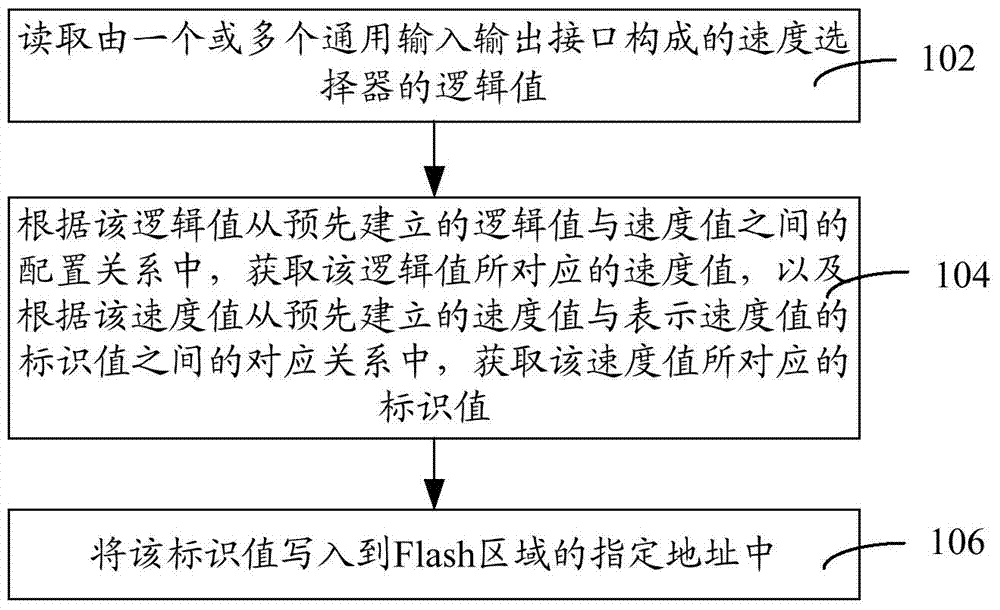

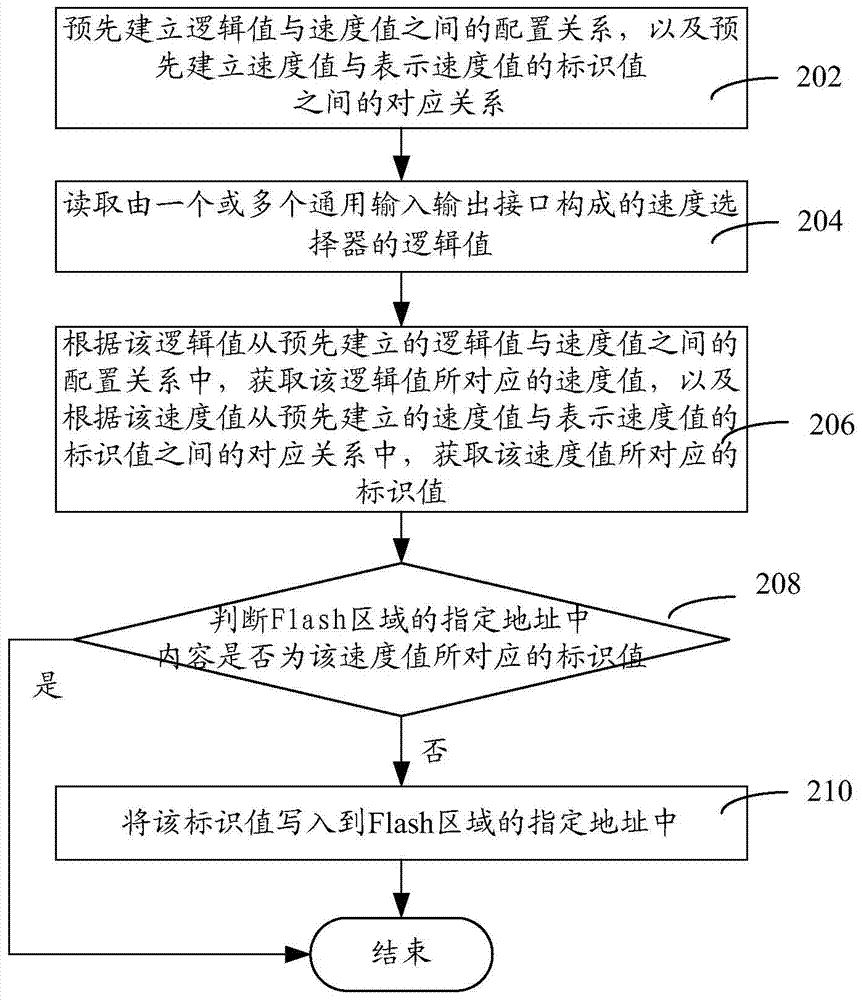

[0033] figure 1 It is a flowchart of a method for adaptively configuring a PCIE bus interface in an embodiment. The method for adaptively configuring the PCIE bus interface comprises the following steps:

[0034] Step 102, read the logic value of the speed selector composed of one or more general input and output interfaces.

[0035] Specifically, there are many types of general purpose input and output interfaces (GPIO for short). In this embodiment, GPIO68 is used to implement, but it is not limited to this, as long as it is an IO interface that can be programmed by software.

[0036] The s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More