Soft landing nanolaminates for advanced patterning

A nano-lamination and patterning technology, applied in nanotechnology, coating, gaseous chemical plating, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] In the following description, numerous specific details are set forth in order to provide a thorough understanding of the presented embodiments. The disclosed embodiments may be practiced without some or all of these specific details. In other instances, well known method operations have not been described in detail in order not to unnecessarily obscure the disclosed embodiments. While the disclosed embodiments will be described in conjunction with specific embodiments, it will be understood that these embodiments are not intended to limit the disclosed embodiments.

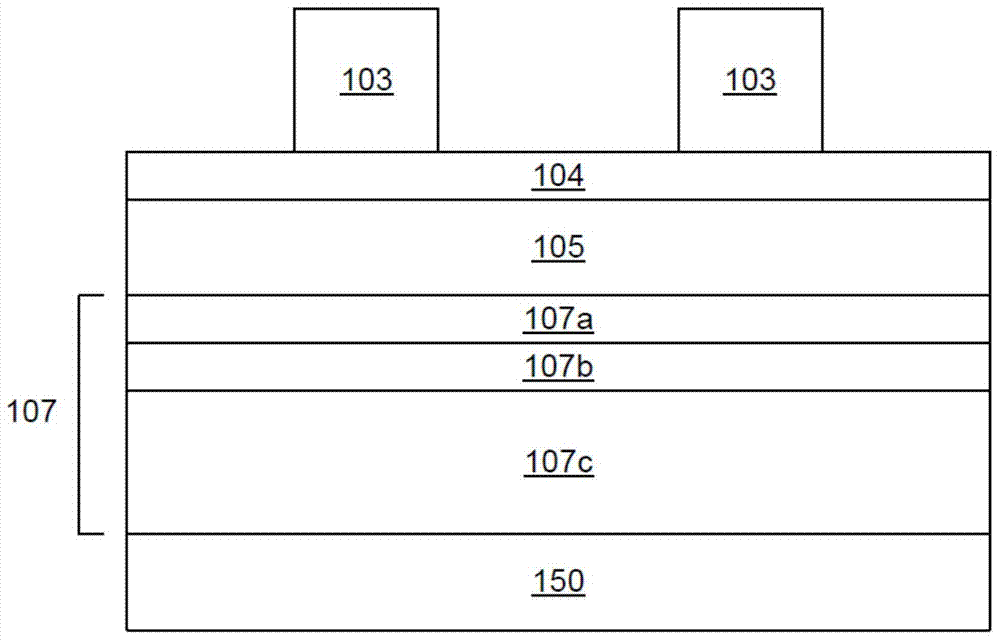

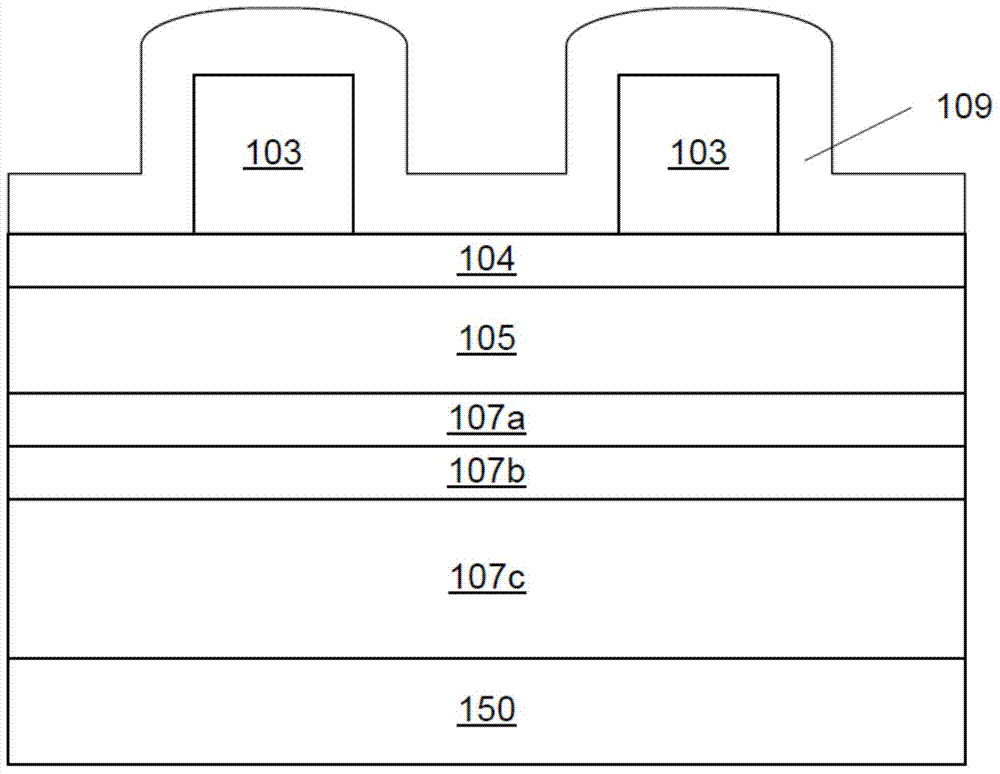

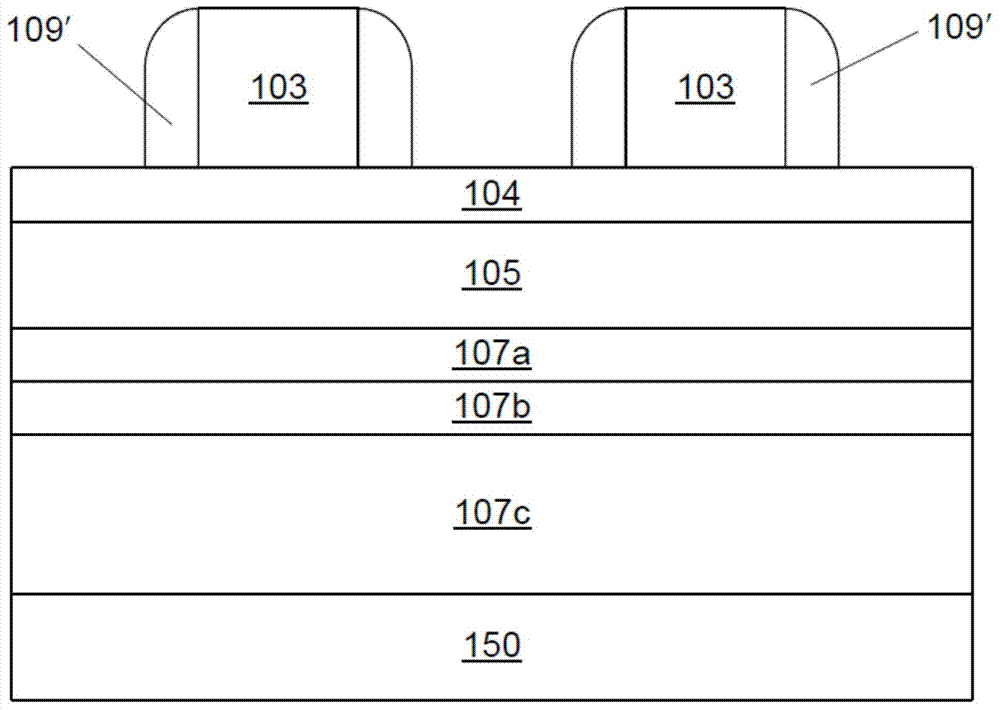

[0028] Fabricating a semiconductor device typically involves depositing one or more thin films in an integrated fabrication process and may include a patterning step. Multi-patterning techniques are used to fabricate advanced integrated circuits, for example, with smaller features or higher aspect ratios or down to 2x or 1x nm nodes. The term "1x" node means a processing node between 10nm and 19nm, and t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More