Fin type field-effect transistor and forming method thereof

A fin field effect and transistor technology, which is applied in semiconductor devices, semiconductor/solid state device manufacturing, electrical components, etc., can solve problems such as uneven distribution of impurity ions and affect the performance of fin field effect transistors, and achieve the effect of improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

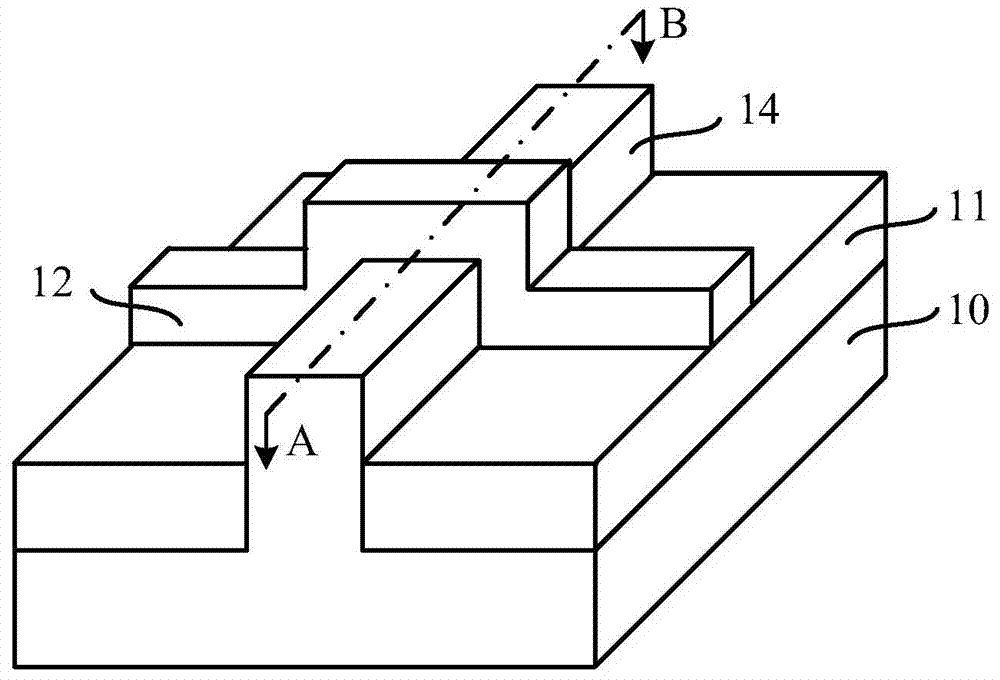

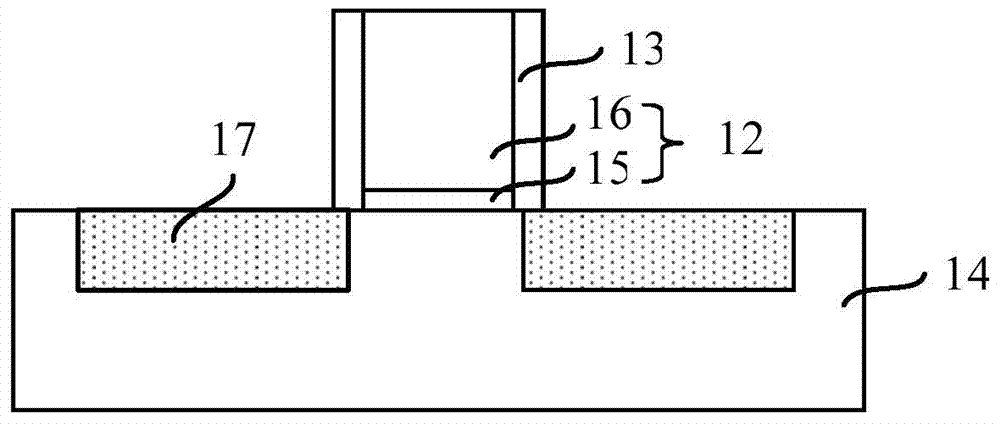

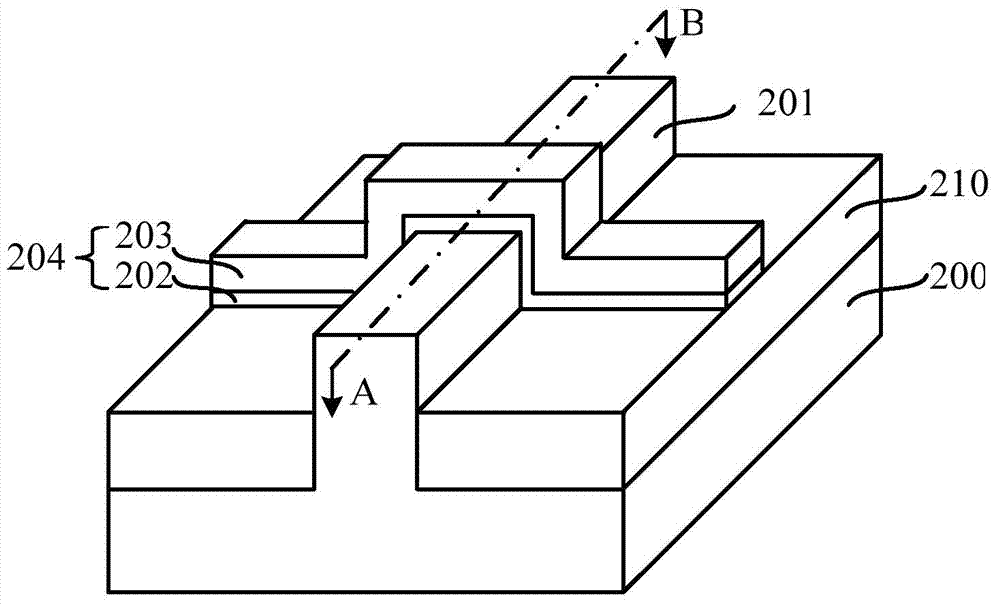

[0034] After research, since the fin is a three-dimensional structure, including a top surface and two side surfaces, when the source / drain region is formed in the fin on both sides of the gate structure by ion implantation, it is very easy to make the formation of the source / drain region The distribution of impurity ions is uneven, for example, the impurity ion concentration at the bottom of the fin (the bottom of the source / drain region) is small, and the top surface and sidewall surfaces of the fins near the gate structure (the top and both sides of the source / drain region There is a large difference in the distribution concentration of impurity ions on the side wall. Since the fin field effect transistor works, the channel is formed on the top surface and the sidewall surfaces on both sides of the fin at the bottom of the gate structure. If the impurity ions are unevenly distributed, the amount of current passing through the channel on the top surface of the fin and the ch...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More