Layout method and device capable of achieving clean supply for chip interior analog modules

An analog module, non-interference technology, used in electrical digital data processing, special data processing applications, instruments, etc., can solve problems such as increasing costs, increasing the number of chip metal layers, wasting chip resources, etc., to improve accuracy and avoid noise coupling. , the effect of reducing costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

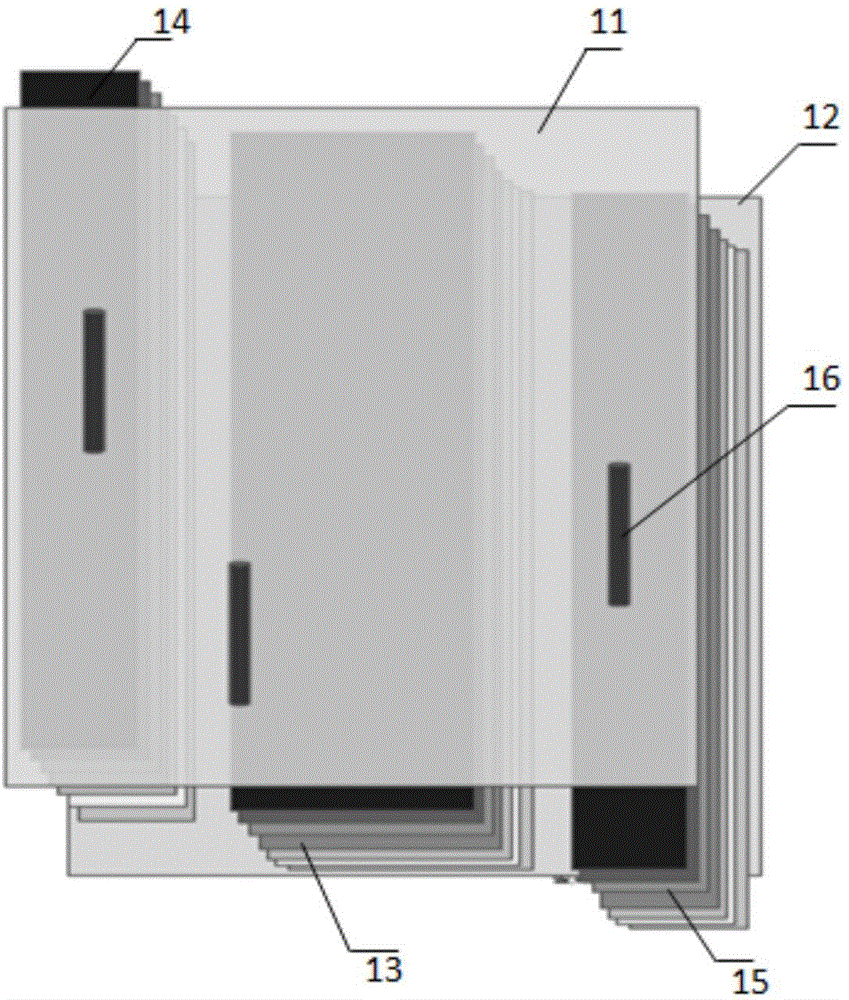

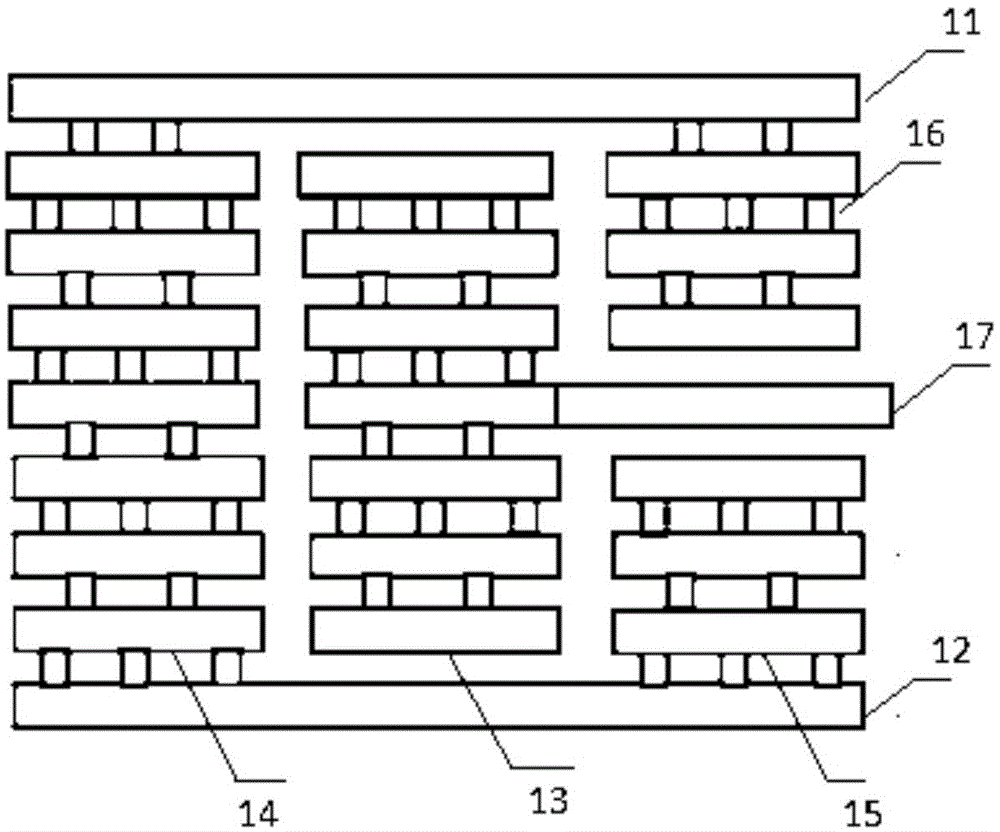

[0014] In order to enable those skilled in the art to better understand the technical solutions in the embodiments of the present invention, and to make the above-mentioned purposes, features and advantages of the embodiments of the present invention more obvious and understandable, the following describes the technical solutions of the present invention through the accompanying drawings and embodiments The technical solution is further described in detail. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

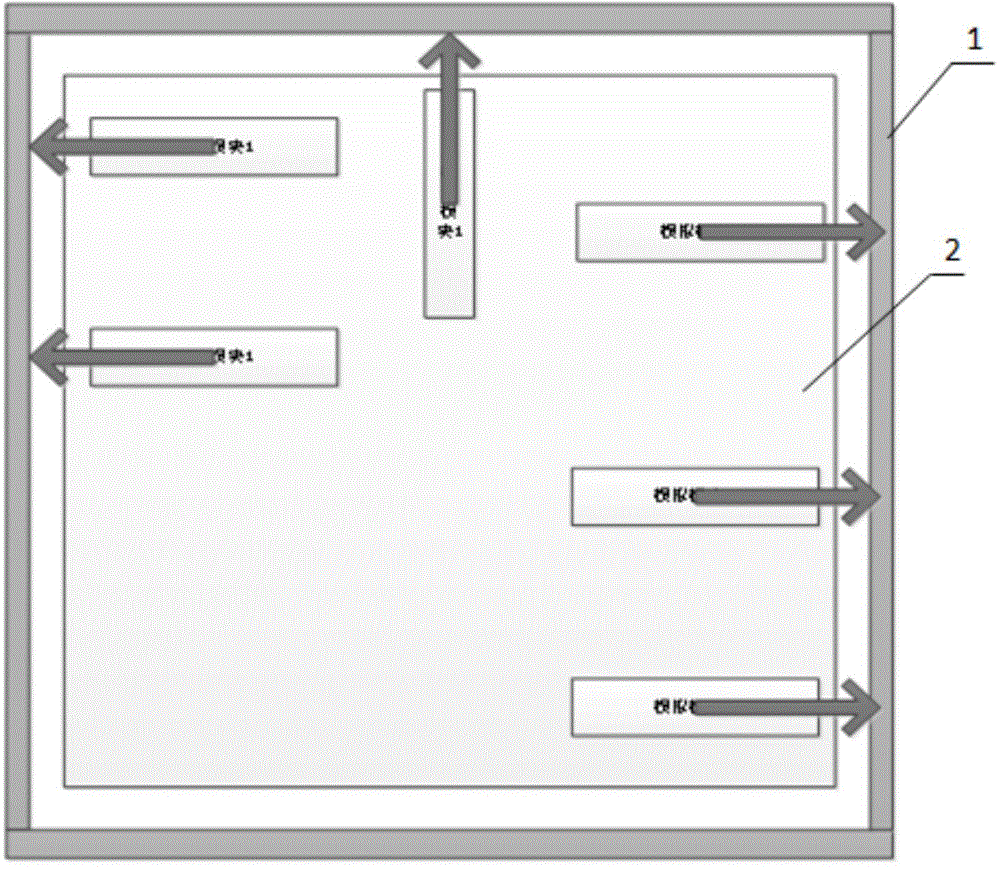

[0015] figure 1 It is a schematic plan view of the layout device to realize the interference-free power supply of the analog module inside the chip.

[0016] Such as figure 1 As shown, the device of the present invention includes a chip 1 and a power ring 2, the chip 1 includes N pieces, and the power ring 2 includes ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More