Phase interpolator control circuit

A phase interpolator and control circuit technology, applied in a single output arrangement and other directions, can solve the problems of discontinuous jump, large clock jitter and data jitter, and achieve the effect of reducing jitter

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The technical solution of the present invention will be further described below in conjunction with the accompanying drawings, but the content protected by the present invention is not limited to the following description.

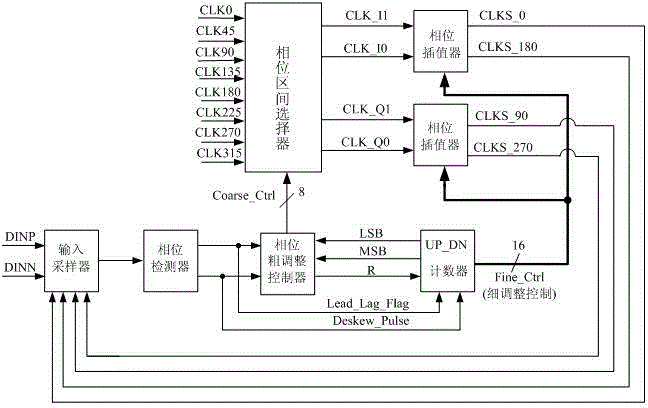

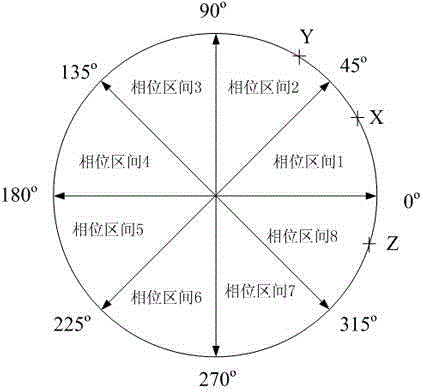

[0022] Such as figure 1 As shown, a phase interpolator control circuit, after sampling and phase detection of the input serial data, realizes phase interpolation by controlling the coarse adjustment and fine adjustment of the phase at the same time, and it includes the following circuit modules:

[0023] Input sampler: Use the sampling clock to sample the input serial data bits and edges, for example, use 2 sets of orthogonal clock signals to sample the input data, 1 set of clock sampling data bits, 1 set of clock sampling data edges, and sample The result is input to the phase detector;

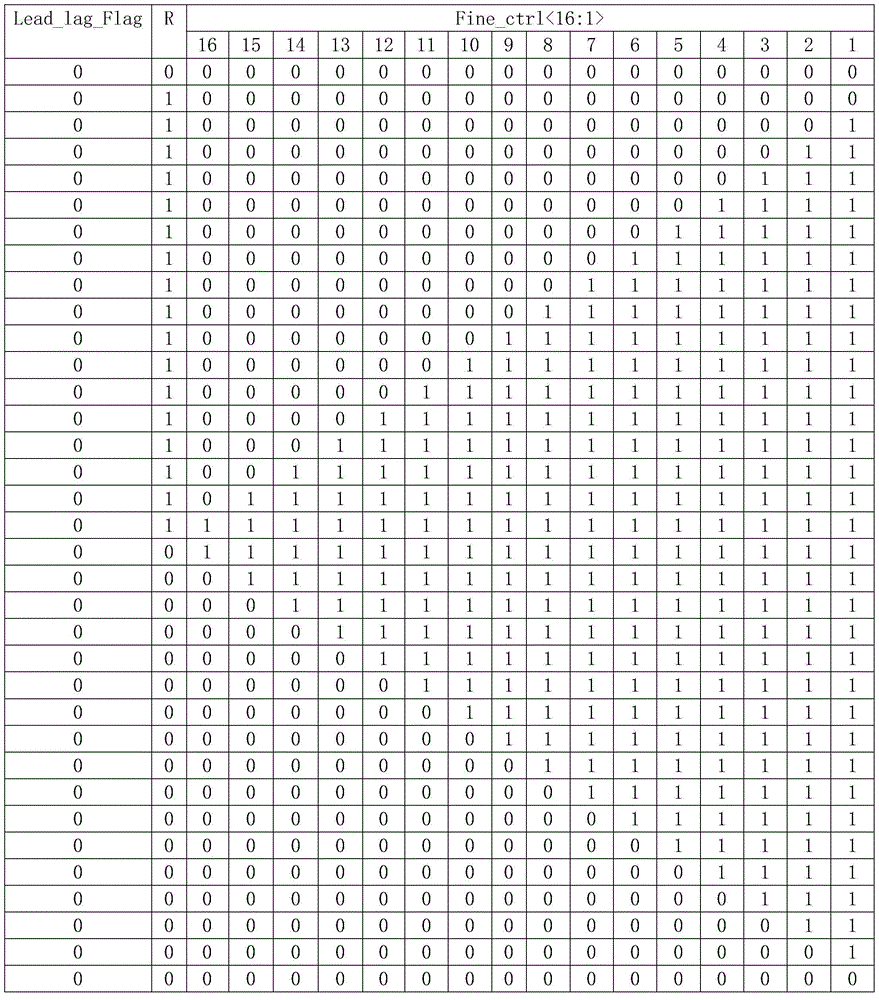

[0024] Phase detector: By detecting the data bits and edges of multi-bit serial data to judge the phase relationship between the sampling clock and the data (inc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com