Array substrate mother plate and manufacture method thereof

A technology for array substrates and manufacturing methods, applied in the field of array substrate motherboards and their manufacture, can solve problems such as inconvenient testing, increased production costs, and inability to solve them in the first place, and achieve the effects of avoiding defective products and saving materials

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. The following examples are used to illustrate the present invention, but are not intended to limit the scope of the present invention.

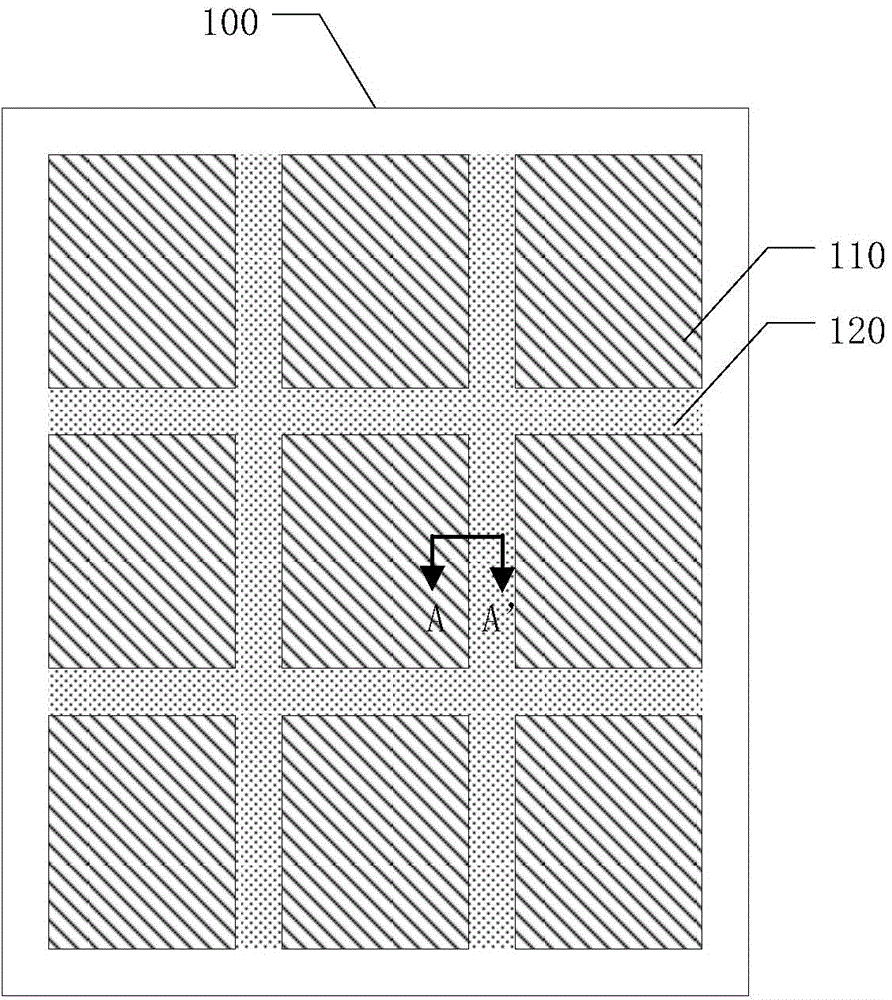

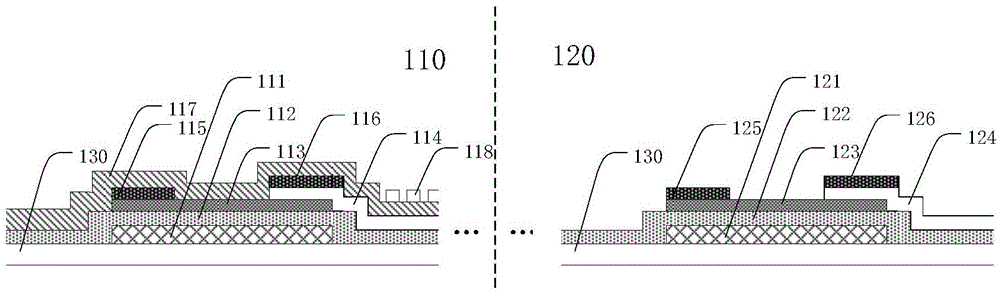

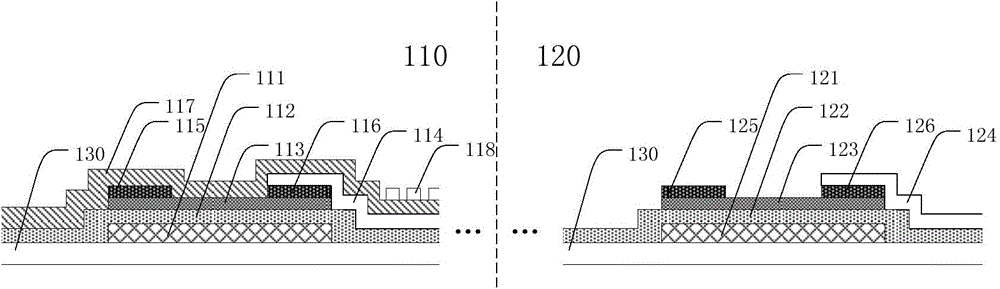

[0023] An embodiment of the present invention provides an array substrate mother board, including a plurality of display areas and a non-display area between any two adjacent display areas, the display area is provided with a first pixel unit for display, A second pixel unit is arranged on the non-display area, and the second pixel unit is used for testing the characteristics of the thin film transistor on the motherboard of the array substrate.

[0024] In the array substrate mother board provided by the embodiment of the present invention, a second pixel unit is set in the non-display area between two adjacent display areas, and the characteristics of the thin film trans...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More