Virtual IO inter-chip connection circuit for FPGAs

An interconnection circuit and chip-to-chip technology, which is applied in the field of FPGA virtual IO chip interconnection circuits, can solve the problems of low IC design verification, high bit error rate transmission, and low bandwidth, so as to reduce the bit error rate, The effect of ensuring accurate transmission, increasing speed and bandwidth

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] In order to make the above objects, features and advantages of the present invention more comprehensible, the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

[0025] One of the core concepts of the embodiments of the present invention is to provide a cross-clock domain-oriented FPGA virtual IO inter-chip interconnection scheme, so that the transmission bandwidth and transmission rate can be arbitrarily increased in a large range, and the error rate can be greatly reduced. The code rate, thus bringing convenience to the operation of the FPGA interconnection interface.

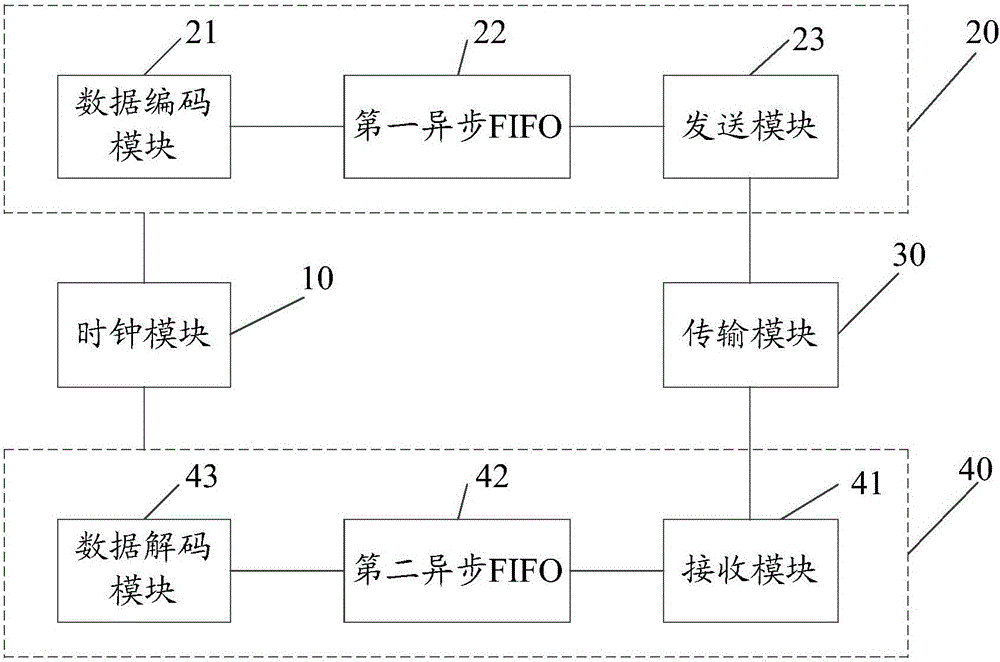

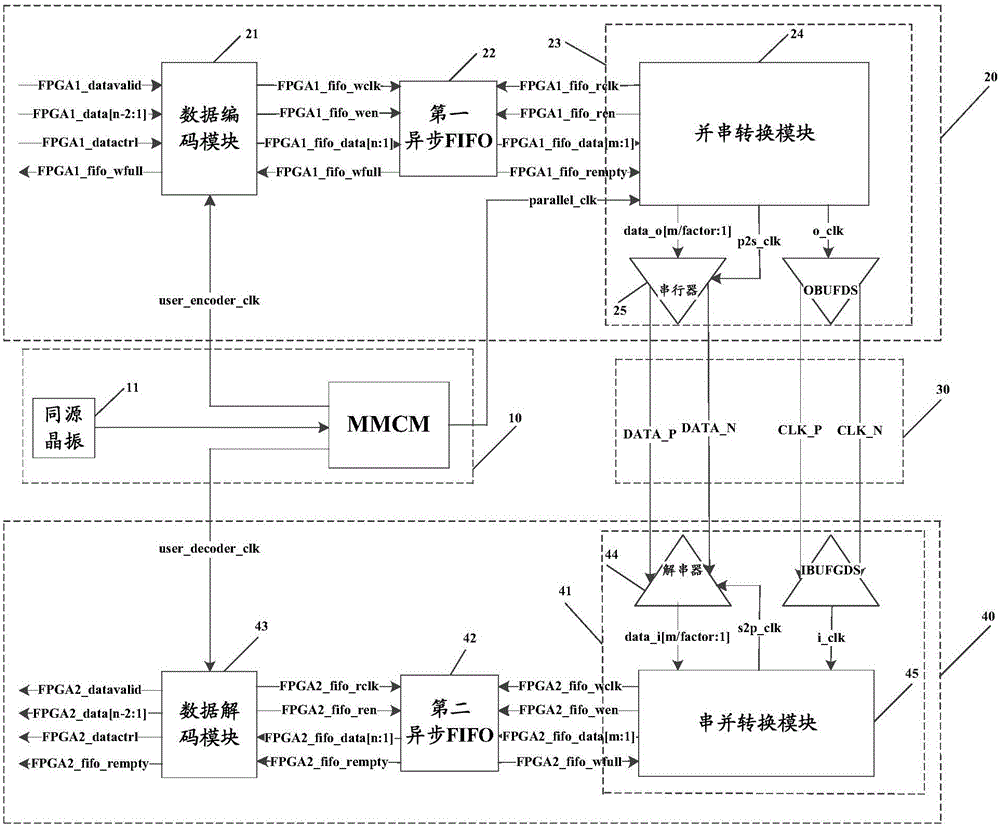

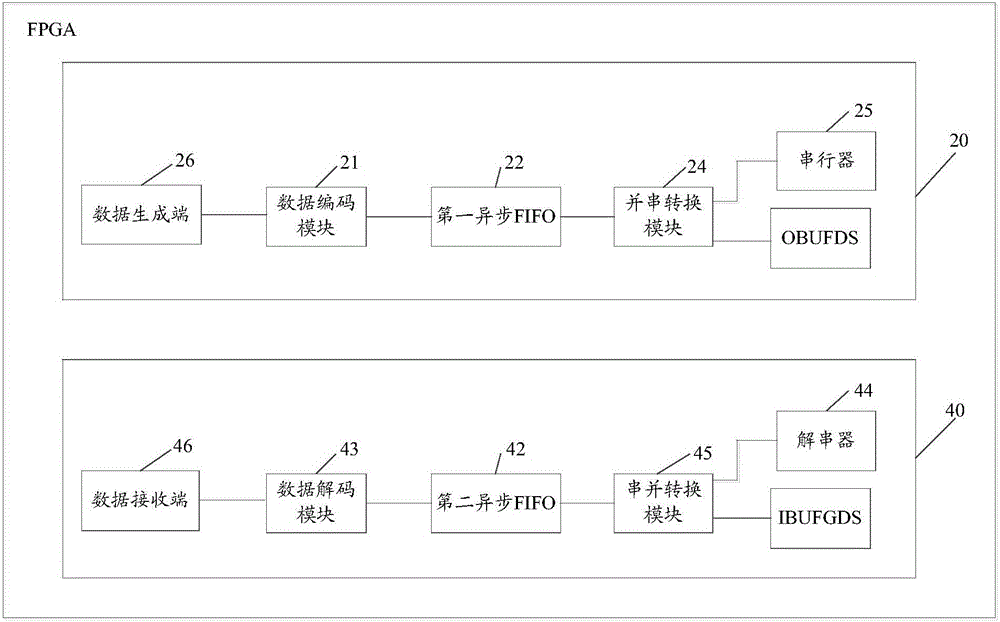

[0026] refer to figure 1 , shows a structural block diagram of a FPGA virtual IO chip interconnection circuit embodiment of the present invention, specifically may include the following modules: clock module 10, sending FPGA end circuit 20 such as FPGA, transmission module 30 and receiving FPGA end circuit 40 For example...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More