Time-interleaved pipeline analog-to-digital converter

An analog-to-digital converter and time interleaving technology, applied in the direction of analog-to-digital converters, etc., can solve the problems of reducing DC gain, increasing the bandwidth of operational amplifiers, and failing to effectively improve the bandwidth of high-speed operational amplifiers.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] The present invention will be further described below in conjunction with the accompanying drawings.

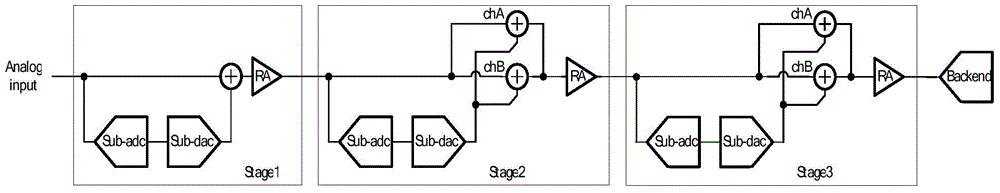

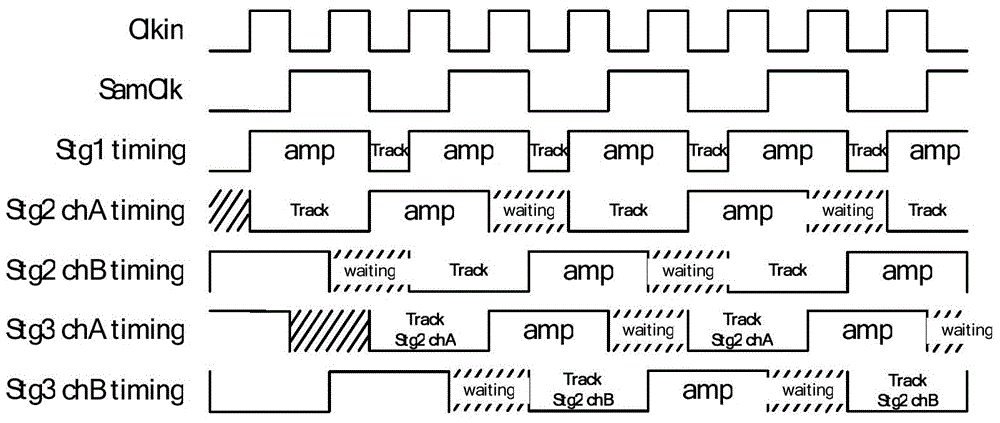

[0021] The circuit structure of the present invention is as figure 1 shown. Contains pipeline Stage1, pipeline Stage2, pipeline Stage3, pipeline Backend. figure 2 are the working phases of the various circuits of the analog-to-digital converter of the present invention.

[0022] The circuit structure of the pipeline Stage1 is the same as that of the traditional pipeline. But its margin amplification phase occupies most of the quantization period. This reduces the power consumption and design difficulty of the operational amplifier of Stage 1 of the pipeline.

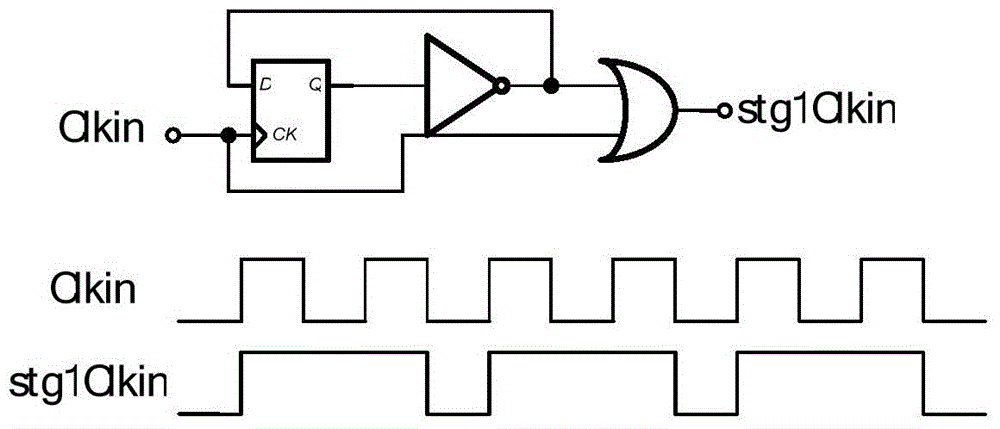

[0023] image 3 It is the circuit used to generate the input clock of the pipeline Stage1, and its input and output waveforms. Clkin is the input clock signal with a frequency equal to twice the sampling rate. stg1Clkin is the input clock of the pipeline Stage1, and generates other clock signals required ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More