3bit streamline-type ADC's sequential control method

A pipelined, timing-controlled technology, applied in signal transmission systems, instruments, electrical components, etc., can solve problems such as ineffectively increasing operational amplifier bandwidth and increasing power consumption, reducing power consumption and area, and reducing the number of stages used , The effect of improving ADC performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments.

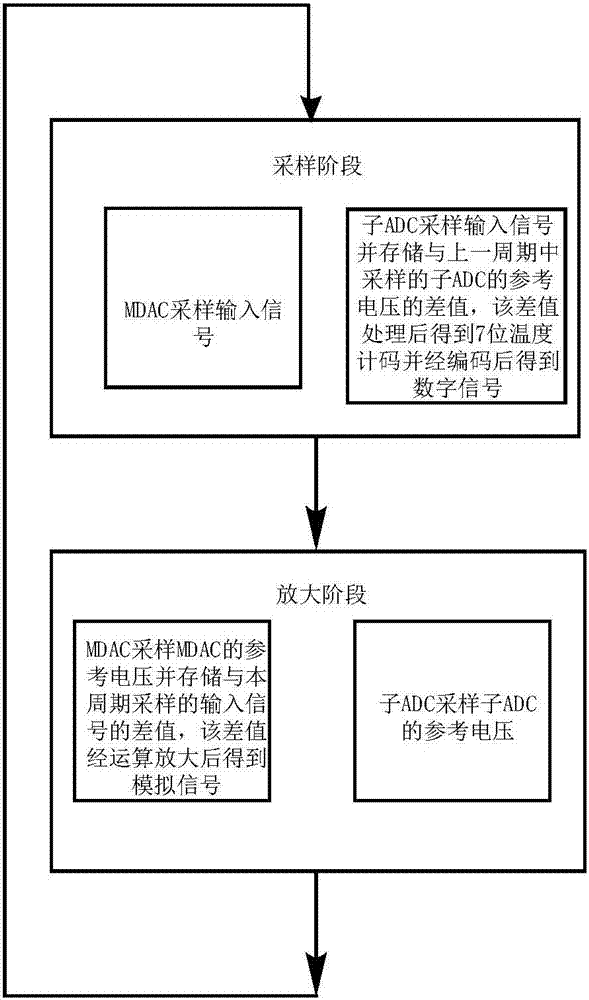

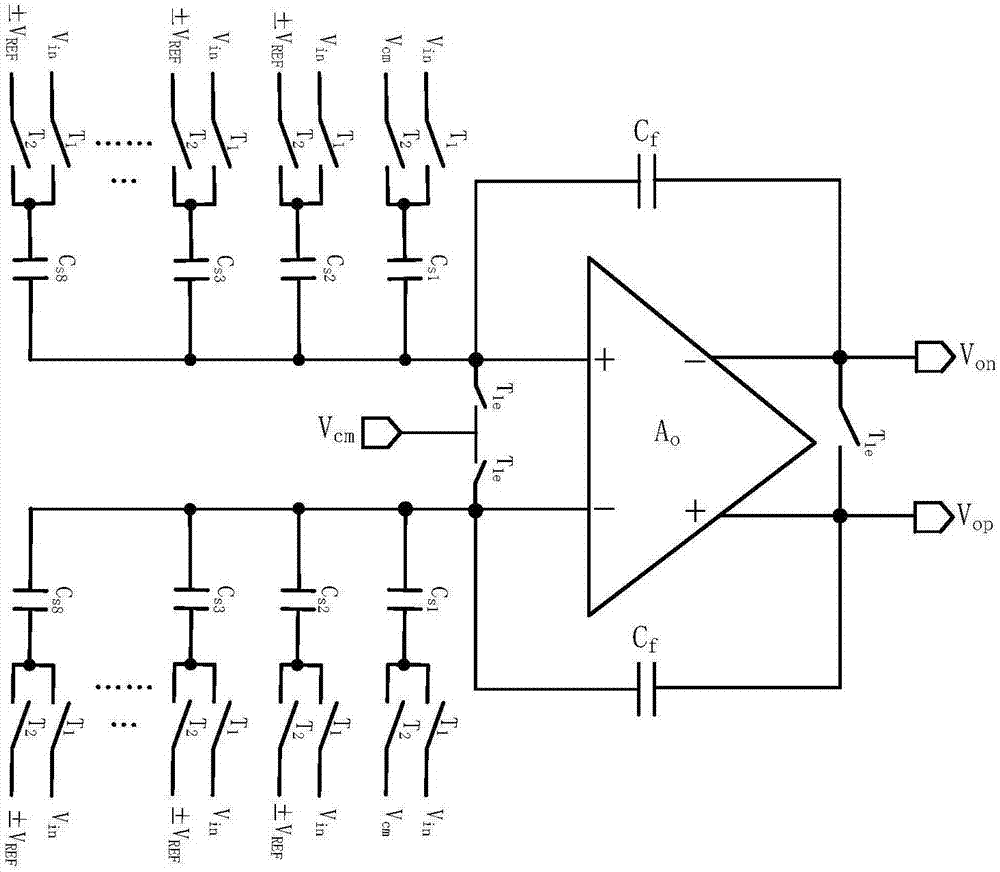

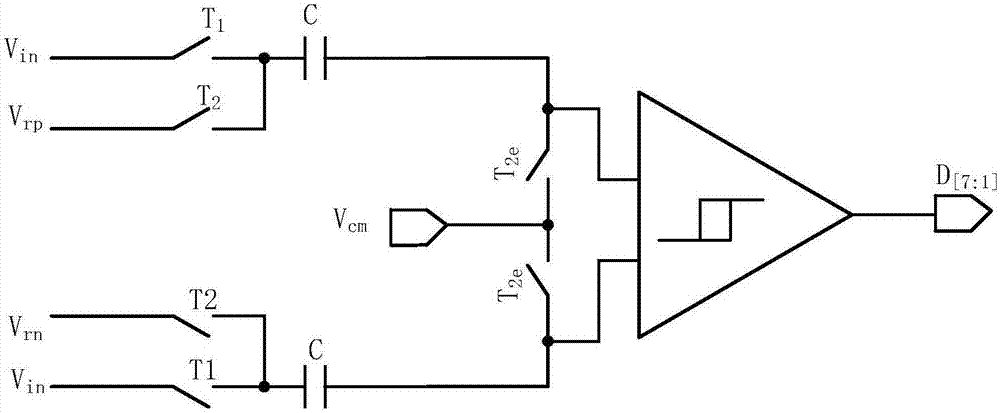

[0028] The 3bit pipelined ADC used in this embodiment includes sub-ADC and MDAC, figure 2 Shown is the structural diagram of MDAC in this embodiment, including an operational amplifier, two feedback capacitors Cf and sixteen sampling capacitors, the two input terminals of the operational amplifier are respectively connected to eight sampling capacitors Cs1-Cs8, wherein the sampling capacitor Cs1 One plate is connected to one input terminal of the operational amplifier, and the other plate is connected to the input signal Vin or the common-mode voltage signal Vcm through a switch; one plate of the sampling capacitor Cs2-Cs8 is connected to one input terminal of the operational amplifier, and the other plate is passed through The switch connects the input signal Vin or the reference voltage ±VREF of the MDAC. The two feedback capacitors Cf ar...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More