LDO circuit

A circuit, capacitor technology, applied in the field of low dropout linear regulator circuit

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

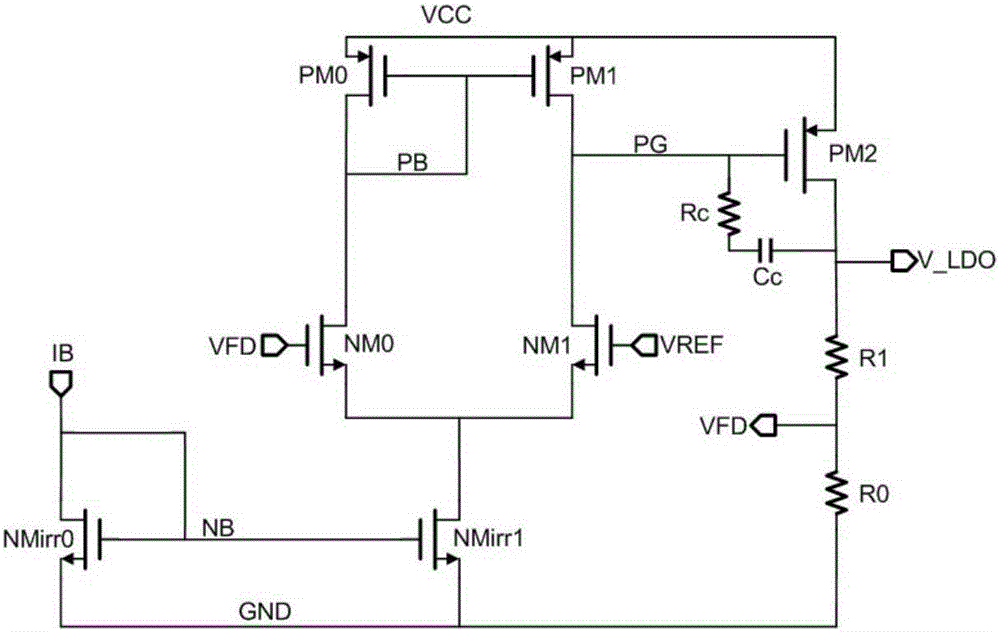

[0035]first review as figure 1 Existing LDO circuit diagram shown; applicant's figure 1 The technical problems existing in the circuit shown are analyzed as follows, figure 1 The circuit shown in the figure only produces LDO output voltage overshoot during power-on, because it takes a certain amount of time for the feedback loop to stabilize, that is, it takes a certain amount of time for the nodes PG and PB to reach a stable value, and the node PG passes through The current flowing out of the PMOS tube PM1 increases the charging of the compensation capacitor Cc. During the power-on process, the current of the PMOS tube PM1 is small, so the charging current of the compensation capacitor Cc is small, so that the node PG rises faster during the power-on process. It should be less than the rising rate of the power supply voltage VCC, so the source-gate voltage of the PMOS transistor PM2 will maintain a large value during the power-on process, so that the PMOS transistor PM2 will...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com