Timer IP (Intellectual Property) core connected with 8-bit microprocessor application system and method thereof for realizing timing control of timer

An application system and microprocessor technology, applied in the direction of machine execution devices, etc., can solve the problems of large circuit scale and heavy maintenance workload

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0174] A timer IP core A that can be set to form six 32-bit timers and connected to an 8-bit microprocessor application system (hereinafter referred to as: timer IP core A):

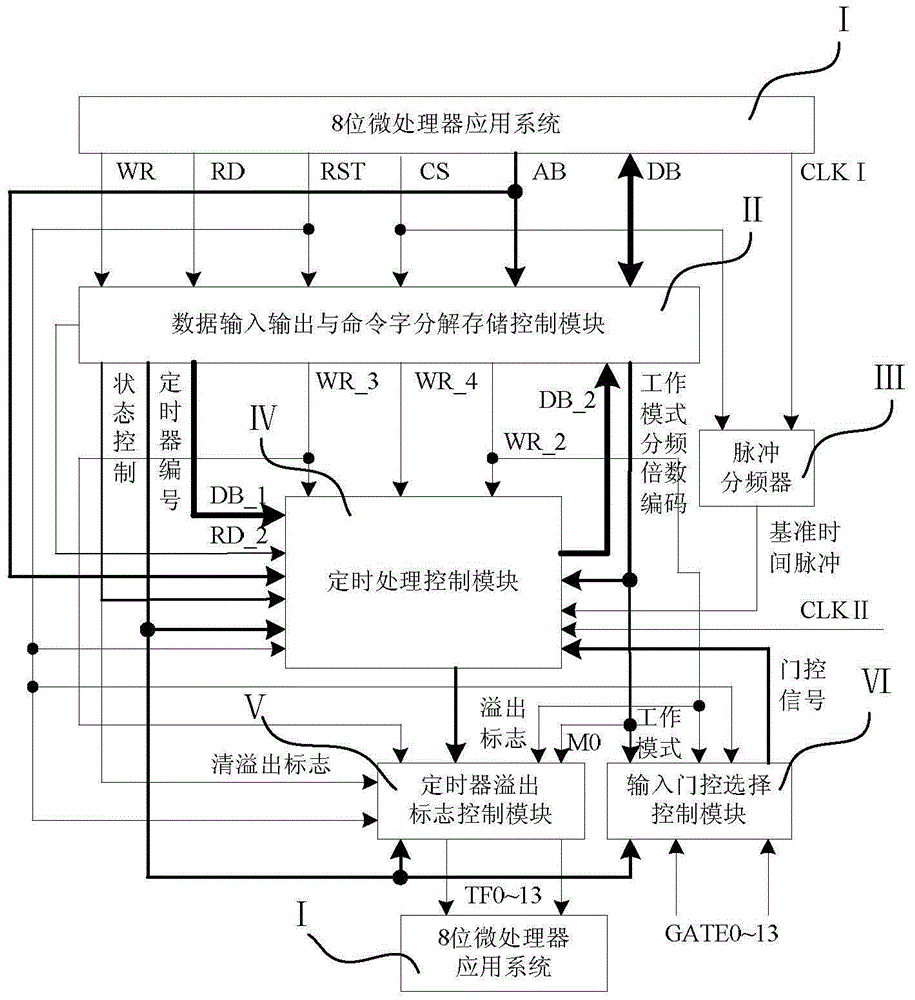

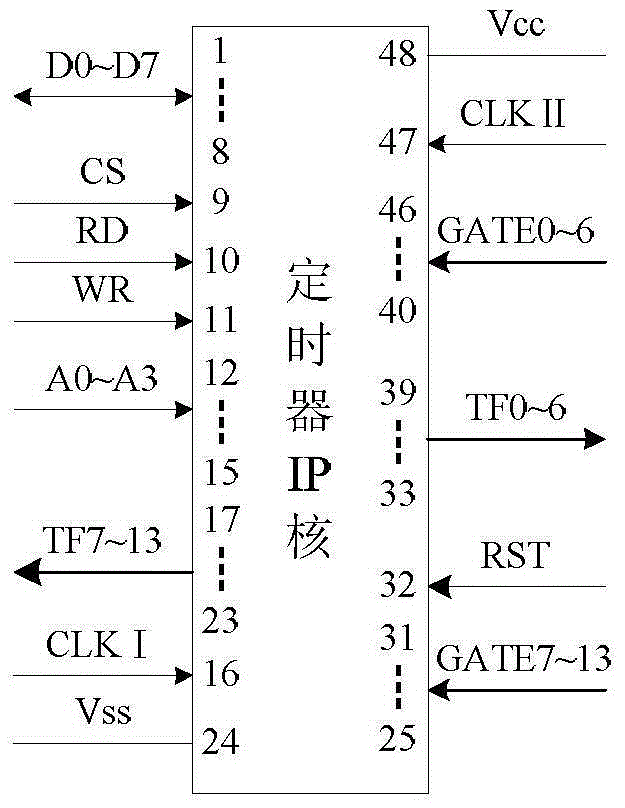

[0175] As mentioned above, the timer IP core A connected with the 8-bit microprocessor application system includes data input and output and command word decomposition storage control module II, pulse 12 frequency divider III, timing processing control module IV, timer overflow flag Control module Ⅴ, input gate selection control module Ⅵ (see figure 1 ), the timer IP core A has 48 pins, its package diagram see figure 2 ;

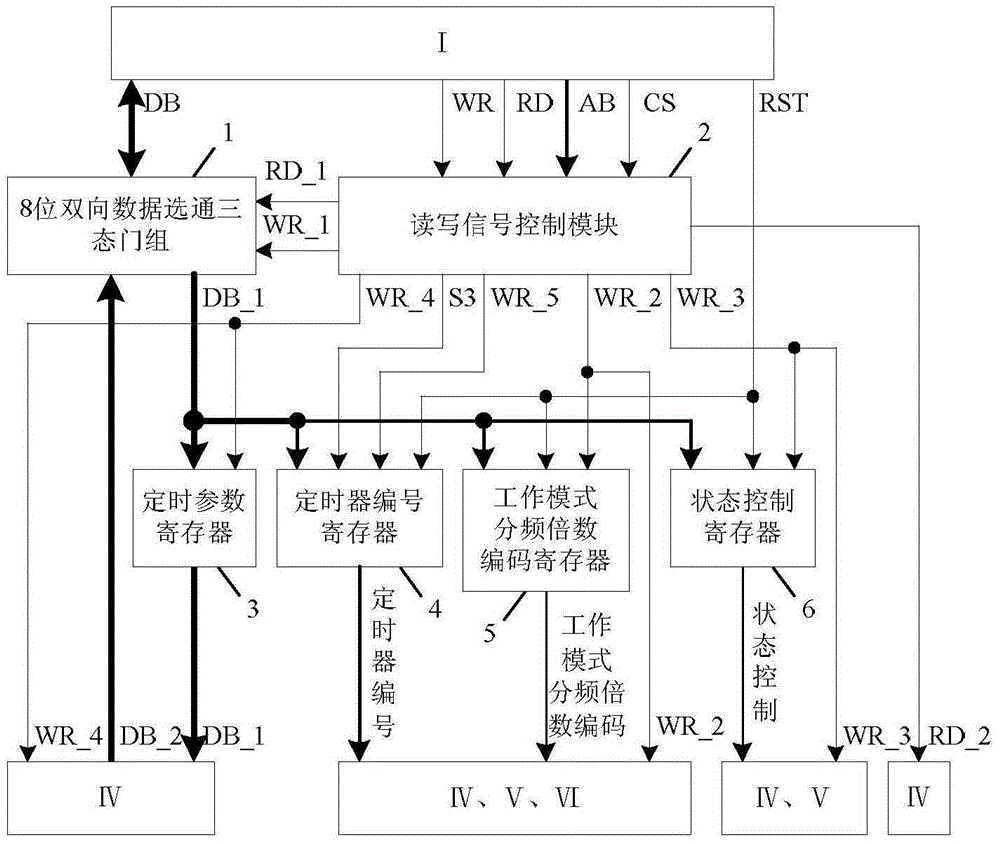

[0176] Such as image 3 As shown, the data input and output and command word decomposition storage control module II includes 8-bit bidirectional data strobe tri-state gate group 1, read and write signal control module 2, timing parameter register 3, timer number register 4, working mode division Frequency multiple encoding register 5, state control register 6;

[0177]The 8-bit b...

Embodiment 2

[0268] A timer IP core B that can be set to form three 32-bit timers and connected to an 8-bit microprocessor application system (hereinafter referred to as: timer IP core B):

[0269] The timer IP core B has 34 pins, the package diagram see Figure 6 ;

[0270] The basic structure of this timer IP core B is the same as embodiment one, and the difference with embodiment one is: this timer IP core B has 7 16-bit timers, and 6 of them can form 3 32-bit timers; The overflow flag output signals TF0~13 of the timer overflow flag control module V are transformed into overflow flag output signals TF0~7, and the gate control input signals GATE0~13 of the input gate selection control module VI are transformed into gate control input signals GATE0 ~7, see figure 1 The connection line of the 4th timer number value S3 and the timer number register 4 of the read-write signal control module 2 of the data input and output and the command word decomposition storage control module II is dele...

Embodiment 3

[0274] A timer IP core connected with an 8-bit microprocessor application system, figure 1 The pulse 12 frequency divider III determines the timing reference clock of the timer IP core, transforms the pulse 12 frequency divider III into a 50 frequency divider III, and adapts to the case where the clock frequency of an 8-bit microprocessor is greater than 12MHz.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More