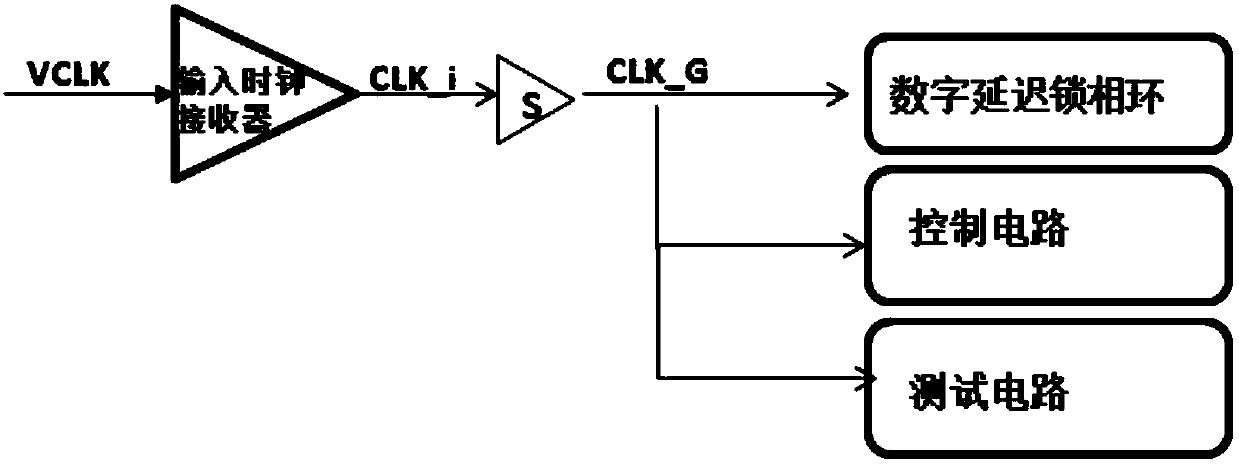

Method, circuit and dram memory for improving input clock duty ratio immunity

A technology of input clock and duty cycle, which is applied in the field of DRAM memory to improve the immunity of input clock duty cycle, can solve the problems of abnormal control circuit function and clock loss, and achieve the effect of improving immunity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

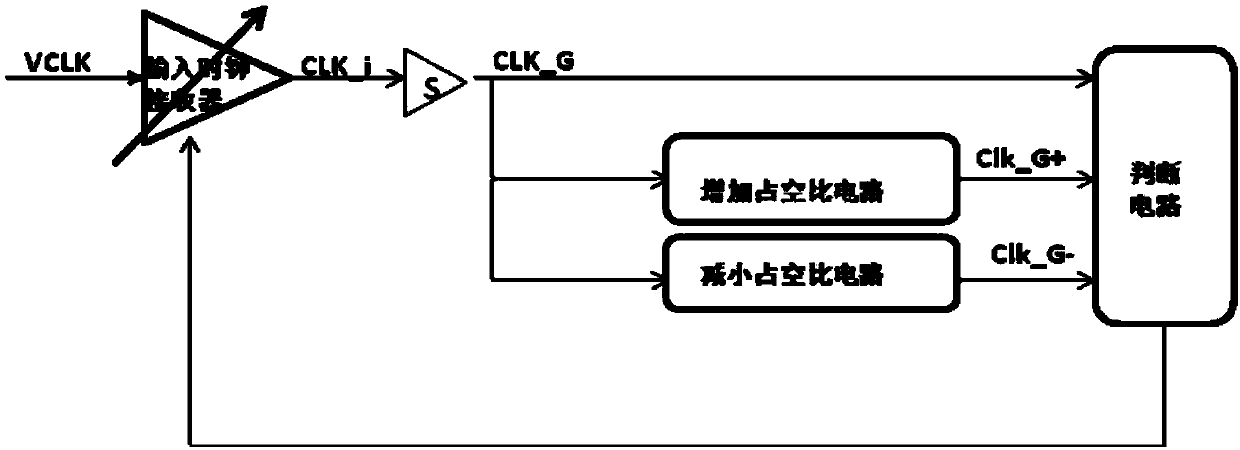

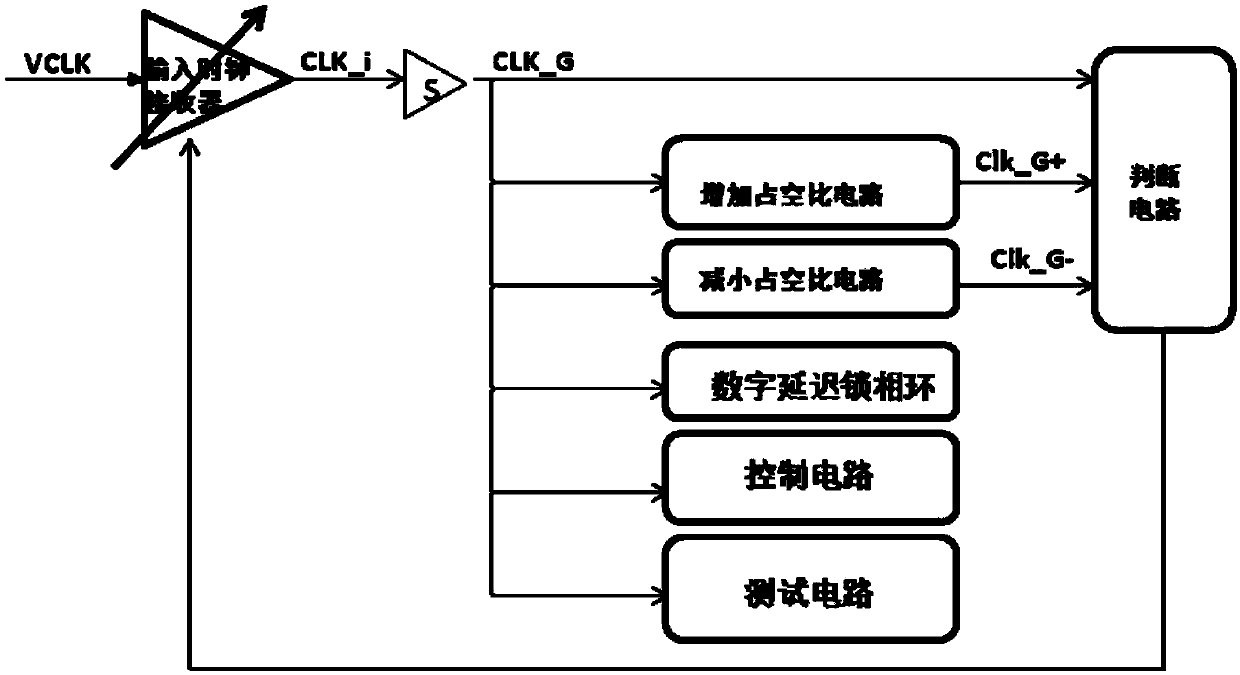

[0036] Such as figure 2 As shown, the circuit for improving the immunity of the input clock duty cycle includes increasing the duty cycle circuit, reducing the duty cycle circuit and judging circuit, and increasing the duty cycle circuit is used to increase the duty cycle of the required clock Clk_G, Obtain increased duty cycle clock Clk_G+; reduce the duty cycle circuit to reduce the duty cycle of the required clock Clk_G to obtain a reduced duty cycle clock Clk_G-; the judgment circuit is used to determine the required clock Clk_G, increase Whether the duty cycle clock Clk_G+ and the reduced duty cycle clock Clk_G- are lost, and adjust the input clock receiver according to the judgment result.

[0037] Generally, increasing the duty cycle circuit includes adjusting the driving tube (it can be realized simply by adjusting the p / n ratio of the driving tube, p is strong and n is weak); reducing the duty cycle circuit includes adjusting the driving tube. It can be realized sim...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More