Method for forming embedded silicon germanium

A technology of embedded silicon germanium and silicon nitride layers, which is applied in the fields of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of eSiGe poor selectivity, poor surface morphology, oxide layer loss, etc. Effects of carrier mobility, suppression of shoulder defects, and increase in driving current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

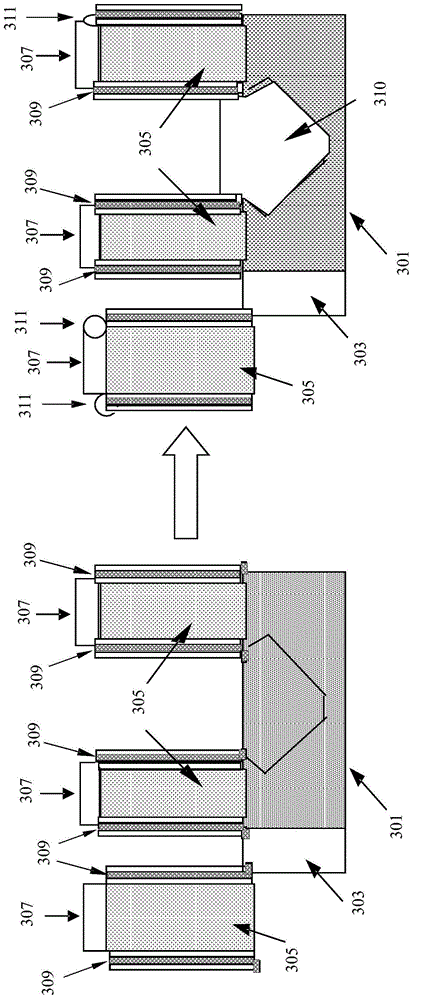

[0063] The present invention will be described in detail below with reference to the accompanying drawings. It should be understood that the following detailed description is merely exemplary in nature and is not intended to limit the embodiments of the subject matter or applications and the uses of these embodiments. As used herein, the word "exemplary" means "serving as an example, instance or illustration". Any implementation described herein as exemplary is not to be construed as necessarily preferred or superior over other implementations. Furthermore, there is no intention to be bound by any expressed or implied theory presented in the preceding technical field, background, brief summary or the following detailed description.

[0064] The terms "first," "second," "third," "fourth," etc., if any, in the description and claims are used to distinguish between similar elements and not necessarily to Describe a specific sequence or chronological order. It is to be understo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More