Array substrate and manufacturing method therefor, display apparatus and mask plate

The technology of an array substrate and a manufacturing method, which is applied in the field of masks, can solve the problems of high manufacturing costs, complex manufacturing processes, and a large number of masks, and achieve the effect of reducing process costs and usage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0047] Specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings. It should be understood that the specific embodiments described here are only used to illustrate and explain the present invention, and are not intended to limit the present invention.

[0048] As an aspect of the present invention, a method for manufacturing an array substrate is provided, including:

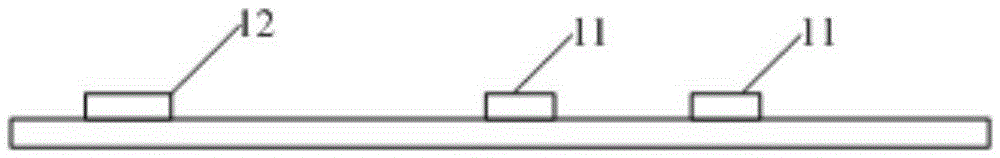

[0049] S1, forming a pattern including gate 11 and gate line 12, such as figure 1 shown;

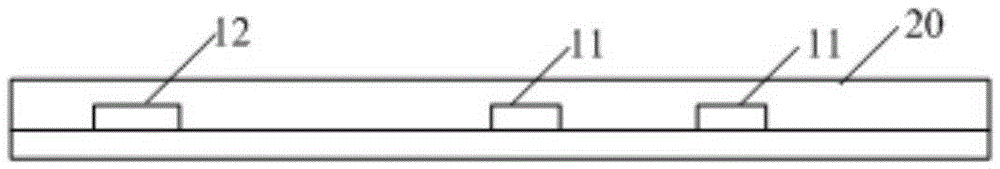

[0050] S2, forming an insulating layer 20, such as figure 2 shown;

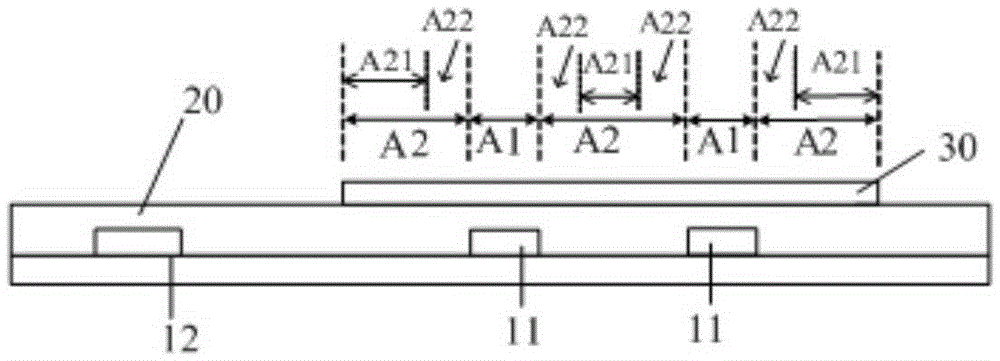

[0051] S3, forming a pattern comprising the active layer 30, such as image 3 As shown, the region where the active layer is located includes a first region A1 corresponding to the gate and a second region A2 located on both sides of the first region A1;

[0052] S4. Form a mask pattern, the mask pattern includes a hollow part, a first part and a second part, the hollow part is used ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com