Semiconductor device, manufacturing method therefor, and electronic device

A technology for semiconductors and devices, applied in the field of semiconductor devices and their preparation, can solve the problems of difficult control of the height of metal gates, uneven height of metal gates, reduced device performance and yield, etc., to improve residual problems, improve uniformity, Improve the effect of control

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

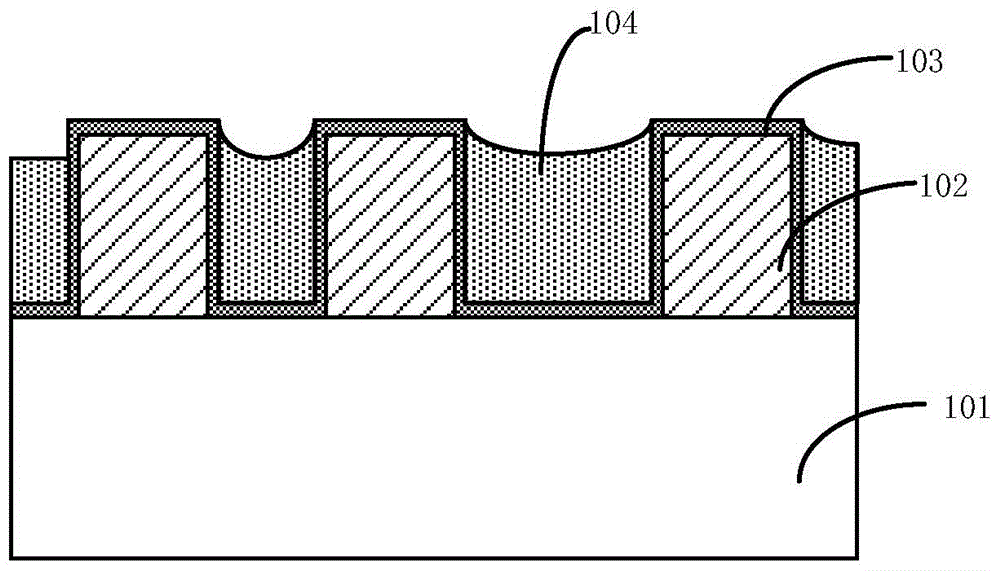

[0037] At present, the fabrication methods of semiconductor devices containing metal gates are as follows: figure 1 As shown, first a substrate 101 is provided, a dummy gate structure 102 is formed on the substrate, and then a spacer layer and / or a contact hole etch stop layer 103 is formed on the substrate 101 and the dummy gate structure 102, and Depositing a FCVD dielectric layer 104 by FCVD (fluid chemical vapor deposition) method on the spacer layer and / or contact hole etch stop layer 103, and then performing dry etching, wet etching and planarization on the FCVD dielectric layer, Wherein the surface of the FCVD dielectric layer 104 is severely recessed after planarization (such as figure 1 As shown), it affects the determination of the end point of the metal gate planarization in the subsequent process, so that the height of the metal gate is difficult to control, resulting in uneven height of the metal gate, which affects the performance and yield of the device.

[003...

Embodiment 2

[0087] The present invention also provides a semiconductor device, which is prepared by the method described in Embodiment 1. The height of the metal grid in the semiconductor device prepared by the method of the present invention is easier to control, and the height is more uniform, which improves the performance and yield of the semiconductor device.

Embodiment 3

[0089]The present invention also provides an electronic device, including the semiconductor device described in Embodiment 2. Wherein, the semiconductor device is the semiconductor device described in Embodiment 2, or the semiconductor device obtained according to the preparation method described in Embodiment 1.

[0090] The electronic device of this embodiment can be any electronic product or equipment such as mobile phone, tablet computer, notebook computer, netbook, game console, TV set, VCD, DVD, navigator, camera, video recorder, voice recorder, MP3, MP4, PSP, etc. , can also be any intermediate product including the semiconductor device. The electronic device according to the embodiment of the present invention has better performance due to the use of the above-mentioned semiconductor device.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More