FPGA-based accelerator card and acceleration method thereof

An accelerator card and accelerator module technology, which is applied in the computer field, can solve the problems of PCI-E bus not having universality and universality, insufficient resources to solve tasks with a large amount of calculation, and limited image processing functions, so as to save processing time , low cost, simple method to achieve the effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0050] The present embodiment provides a kind of acceleration method based on FPGA accelerator card, comprises following process:

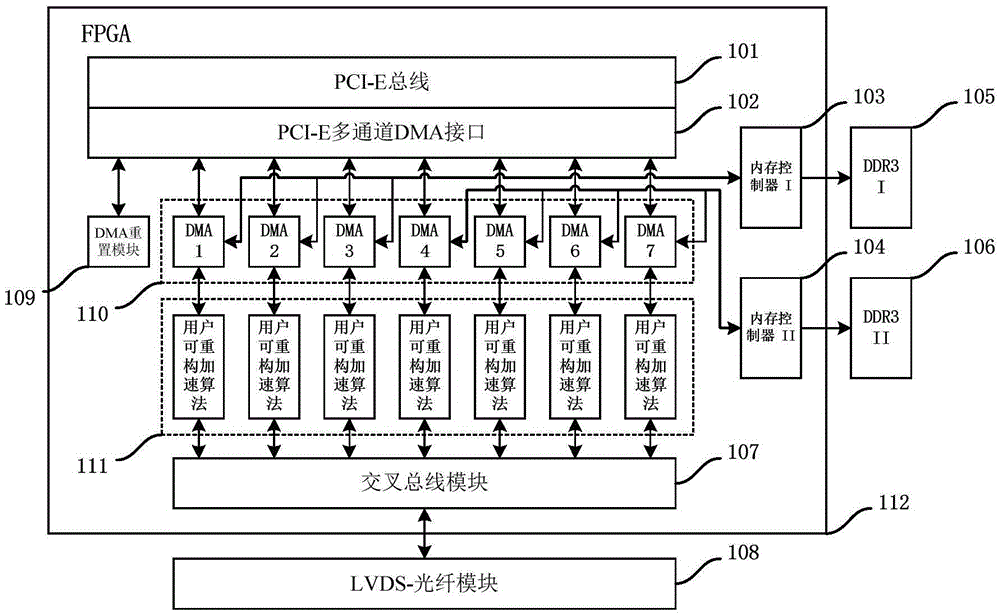

[0051] Build PCI-E bus interface module, multiple DMA, DMA reset module, multiple user reconfigurable acceleration modules, LVDS-fiber module, cross bus module and DDR3 control module inside FPGA.

[0052] The specific method is:

[0053] A PCI-E bus interface module is built inside the FPGA, and the PCI-E bus interface module includes a PCI-E bus and a PCI-E multi-channel DMA interface. The outside of the PCI-E bus interface module is connected to the PC through the PCI-E bus, and the inside of the PCI-E bus interface module uses a unified PCI-E multi-channel DMA interface to connect with multiple DMAs. It mainly supports read and write access to the memory controller by other DMAs inside the FPGA, and supports byte misalignment.

[0054] Multiple DMAs are constructed inside the FPGA, and the DMAs are connected to the PCI-E bus interface module...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More