Fan-out type 3D packaging structure embedded in silicon substrate

A packaging structure and silicon substrate technology, applied in semiconductor/solid-state device components, semiconductor devices, electrical components, etc., can solve problems such as thermal expansion coefficient mismatch, achieve good reliability, achieve miniaturization, and easy miniaturization effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] In order to understand the technical content of the present invention more clearly, the following examples are given in detail, the purpose of which is only to better understand the content of the present invention but not to limit the protection scope of the present invention. The components in the structures in the drawings of the embodiments are not scaled according to the normal scale, so they do not represent the actual relative sizes of the structures in the embodiments.

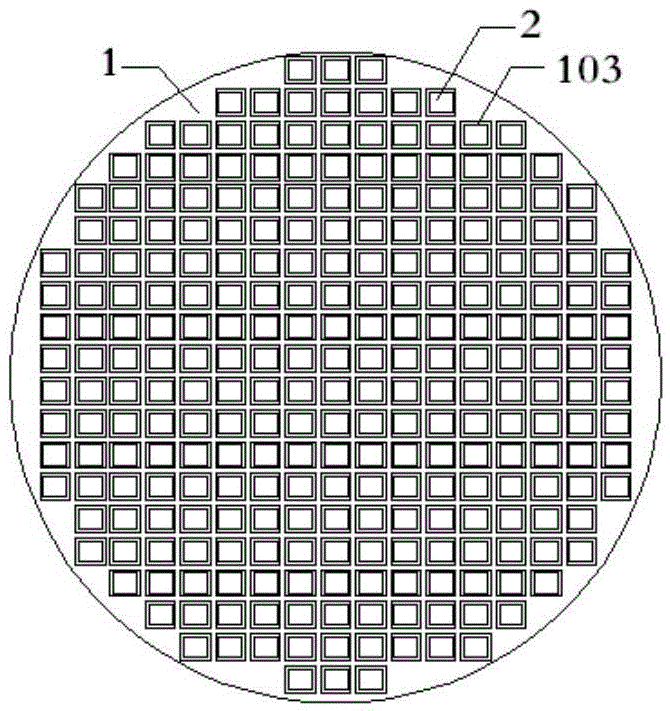

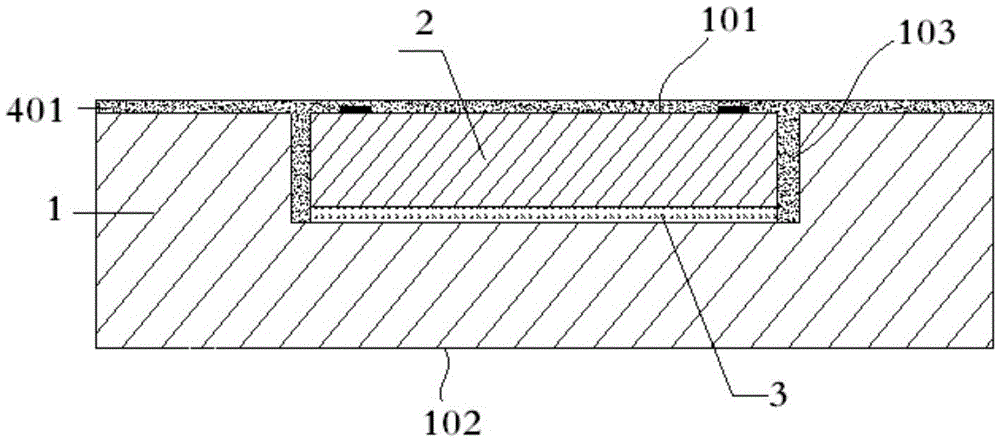

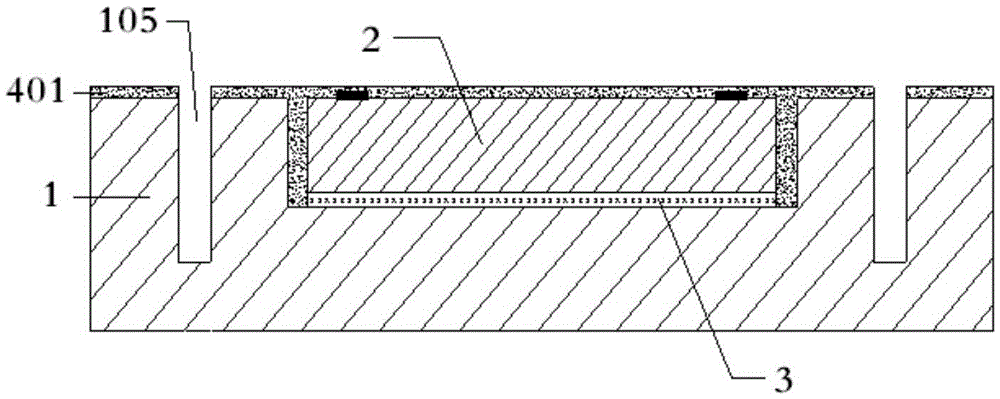

[0038] Such as Figure 11As shown, a fan-out 3D packaging structure embedded in a silicon substrate includes a silicon substrate 1 and at least one functional chip 2 . The silicon substrate 1 encloses other surfaces of the functional chip without the functional surface through the groove 103. There is an adhesive layer between the functional chip 2 and the silicon substrate 1, and there are several vertical conductive through holes 104 near the groove on the silicon substrate 1. At least one pa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More