SRAM type FPGA trigger single-event upset resistance performance assessment system and method

An anti-single event effect and trigger technology, applied in the direction of instruments, measuring devices, measuring electricity, etc., can solve the problems of inaccuracy, complex realization, missed judgment, etc., to simplify the test process, enhance the accuracy and reliability, and improve the The effect of trial efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

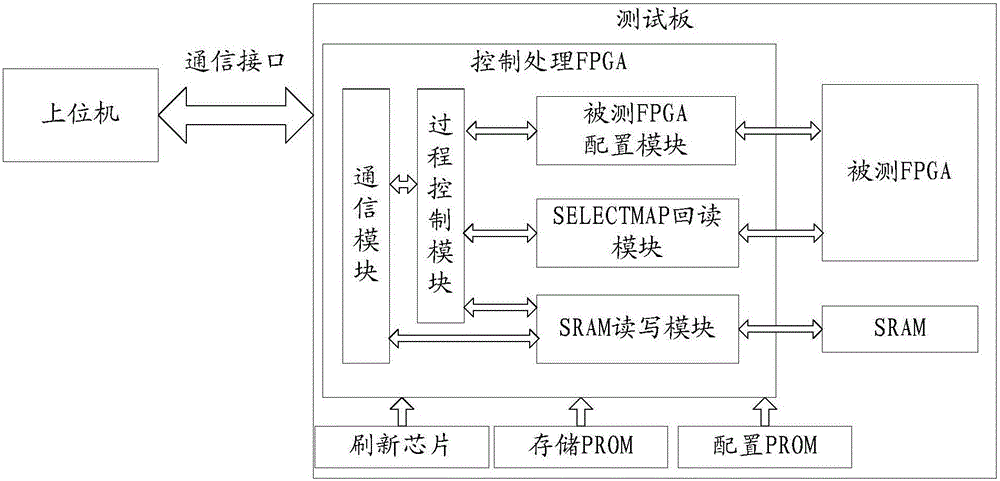

[0025] Such as figure 1Shown, a kind of SRAM type FPGA flip-flop anti-single event effect performance evaluation test system of the present invention comprises host computer and test board; The host computer is placed in the test monitoring room, is used for carrying out test setting, test process control and test result display The test board is placed in the irradiation laboratory; the test board includes a control processing FPGA, a configuration PROM, a refresh chip, a storage PROM, a SRAM and a tested FPGA; , Configuration PROM, connected to the communication interface; the control processing FPGA is connected to the host computer through the communication interface; the storage PROM is used to store the test code stream used to configure the tested FPGA for reading by the refresh chip; the configuration PROM is used to store configuration control processing FPGA configuration code stream; the tested FPGA is placed in the irradiation test area; the control processing FPGA...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More