System-level wafer packaging structure and packaging method

A wafer packaging and system-level technology, applied in the direction of electrical components, electrical solid devices, circuits, etc., can solve the problems of long process flow, low efficiency, slow speed, etc., to reduce process steps, improve production efficiency, and improve production quality. rate effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The present invention will be further described below in conjunction with accompanying drawing.

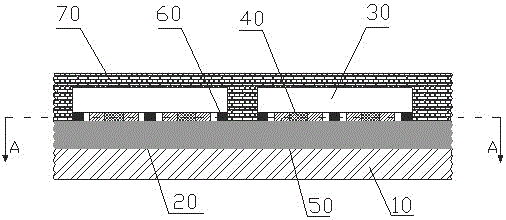

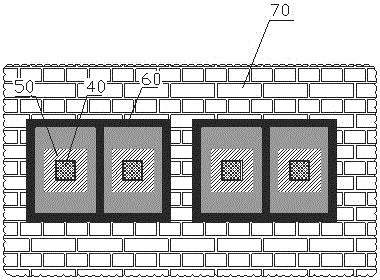

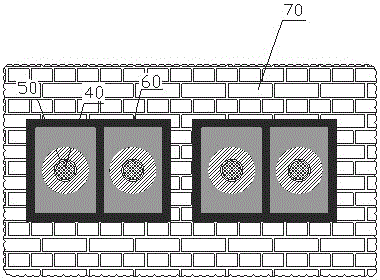

[0025] see figure 1 , a system-on-wafer package structure, including a substrate wafer 10 formed with circuits, the substrate wafer may be a single-layer wafer or a multi-layer stacked wafer in which multiple wafers are bonded together; The interposer 20 arranged on the substrate wafer 10; a plurality of functional chips 30 of uniform height arranged on the interposer 20; also includes a package 70 for packaging a plurality of functional chips, the package 70 may be a plastic, metal or ceramic cover.

[0026] The key point of the present invention is that: the lower surface of the functional chip 30 and the upper surface of the adapter board 20 are also respectively formed with positioning bumps 40 and positioning grooves 50 or positioning grooves 50 and positioning bumps 40, which are used in the placement process. The functional chip 30 is fastened and fixed on the adap...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com