Location method of failure point and failure analysis method of chip

A positioning method and a technology for positioning chips, which are applied in the direction of analyzing materials, using wave/particle radiation for material analysis, instruments, etc., can solve the problems of no solution, inability to determine the location of the failure point of the device, etc., and achieve the effect of reducing the impact

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

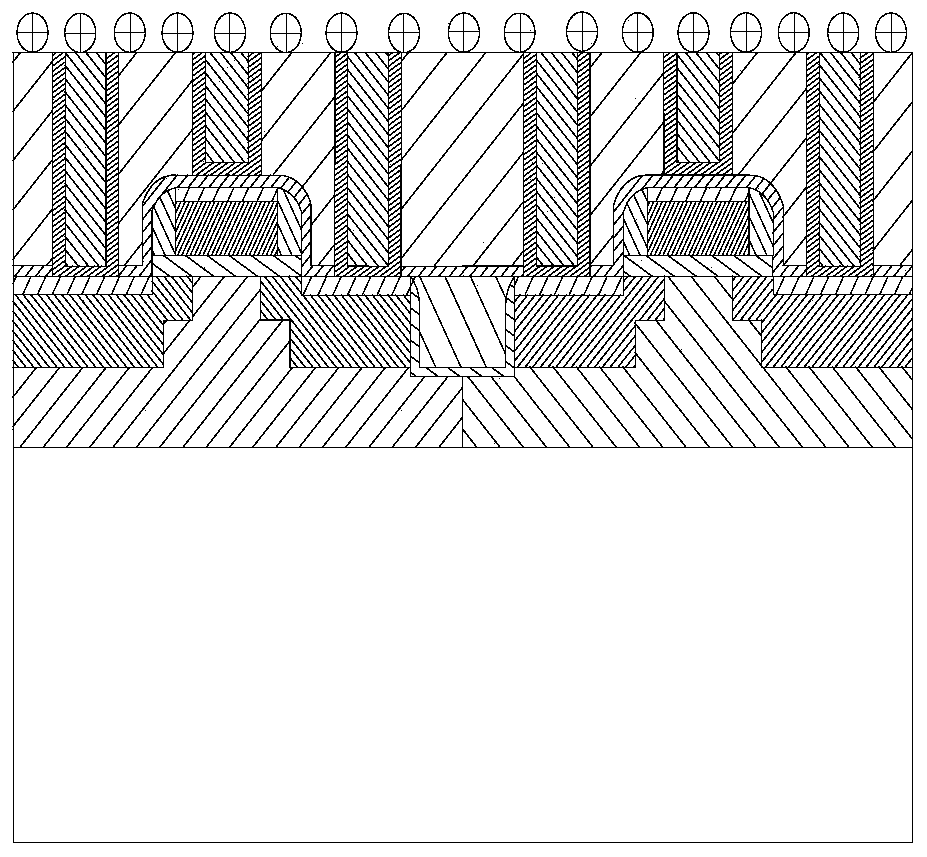

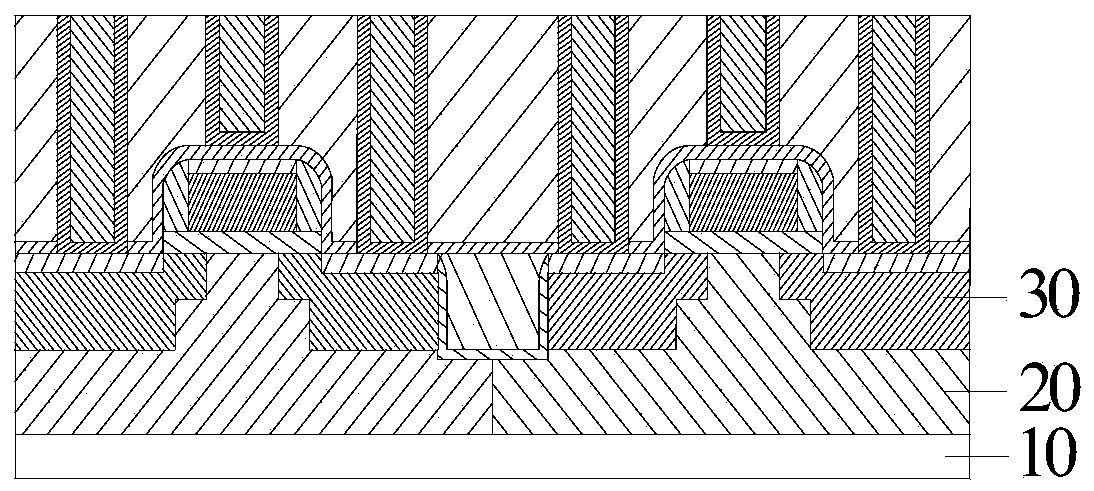

[0048] This embodiment provides a method for locating a failure point, including the following steps:

[0049] Firstly, the back of the chip is chemically mechanically polished so that the thickness of the substrate in the chip is 200nm; then, the back of the chemically mechanically polished chip is bombarded with an ion beam, the ion beam voltage is 150kV, and the bombardment particles are boron ions. The time is 10s, so that the ion beam passes through the devices in the chip; finally, the front side of the chip is peeled off to the surface to be tested, and then the front side of the chip is scanned by an electron beam with an accelerating voltage of 1kV in a scanning electron microscope to obtain a SEM. image, and use the lightness and darkness in the SEM image to determine the location of the failure point in the chip.

Embodiment 2

[0051] This embodiment provides a method for locating a failure point, including the following steps:

[0052] First, the back of the chip is chemically mechanically polished so that the thickness of the substrate in the chip is 300nm; after that, the back of the chip is subjected to vibration treatment with ultrasonic waves, and the time of the vibration treatment is 60s; Rinse the back of the chip, and use an air gun to dry the back of the rinsed chip; then, bombard the back of the chemically mechanically polished chip with an ion beam, the ion beam voltage is 200kV, and the bombarded particles are phosphorus ions. The bombardment time is 60s, so that the ion beam passes through the devices in the chip; finally, the front side of the chip is peeled off to the surface to be tested, and then the front side of the chip is scanned by an electron beam with an accelerating voltage of 1.5kV in the scanning electron microscope to A SEM image is obtained, and the position of the fail...

Embodiment 3

[0054] This embodiment provides a method for locating a failure point, including the following steps:

[0055] First, the back of the chip is chemically mechanically polished so that the thickness of the substrate in the chip is 310nm; then, the back of the chip is subjected to vibration treatment with ultrasonic waves, and the time of the vibration treatment is 300s, and then deionized water is used to deionize the substrate after the vibration treatment. Rinse the back of the chip, and use an air gun to dry the back of the rinsed chip; then, bombard the back of the chemically mechanically polished chip with an ion beam, the ion beam voltage is 210kV, and the bombardment particles are argon atoms. The bombardment time is 65s, so that the ion beam passes through the devices in the chip; finally, the front side of the chip is peeled off to the surface to be tested, and then the front side of the chip is scanned by an electron beam with an accelerating voltage of 2kV in the scann...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More