Graphical silicon-on-insulator substrate material and preparation method thereof

A technology of silicon-on-insulator and substrate materials, which is applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc. Scattering and other problems, to achieve the effect of simple structure and method, ensure material quality, and improve reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

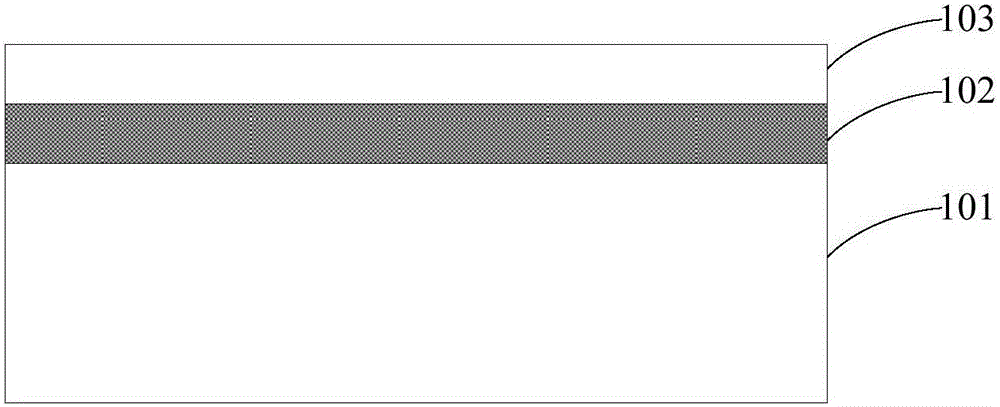

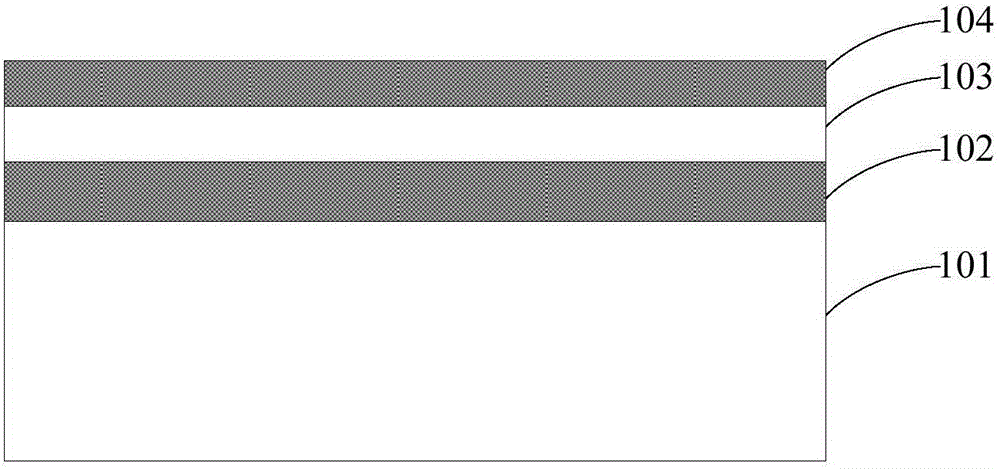

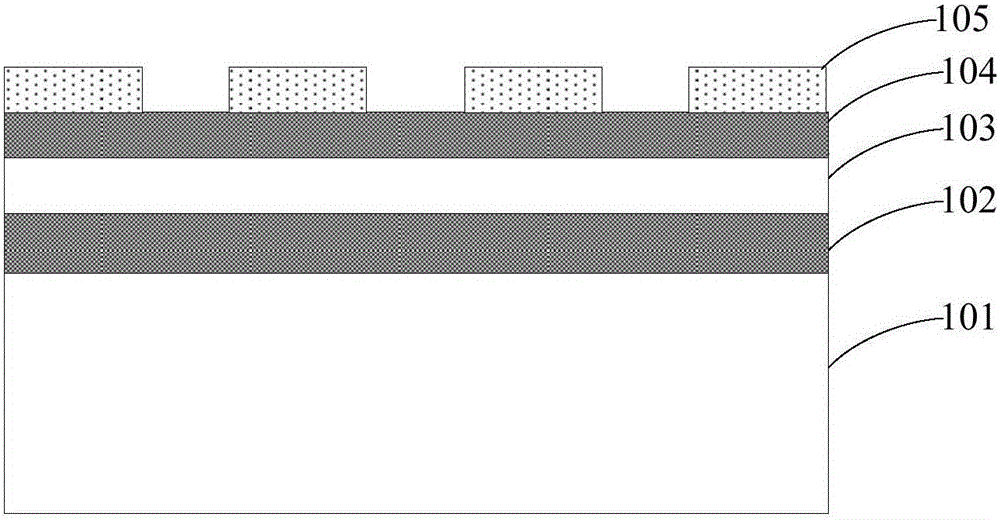

[0038] Embodiments of the present invention are described below through specific examples, and those skilled in the art can easily understand other advantages and effects of the present invention from the content disclosed in this specification. The present invention can also be implemented or applied through other different specific implementation modes, and various modifications or changes can be made to the details in this specification based on different viewpoints and applications without departing from the spirit of the present invention.

[0039] see Figure 1 to Figure 7 . It should be noted that the diagrams provided in this embodiment are only schematically illustrating the basic idea of the present invention, so that only the components related to the present invention are shown in the diagrams rather than the number, shape and Dimensional drawing, the type, quantity and proportion of each component can be changed arbitrarily during actual implementation, and the ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More