Multi-core processor system, allocation program, control program, allocation method, and control method

A technology of multi-core processor and control method, applied in the direction of program control design, multi-program device, resource allocation, etc., can solve the problem of load concentration and achieve the effect of low power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

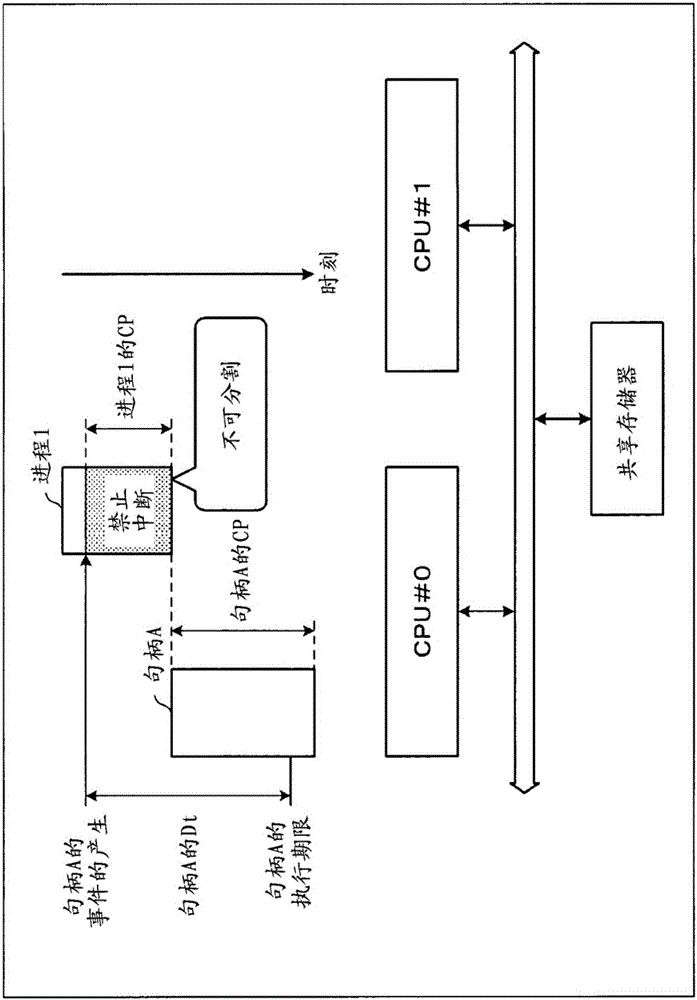

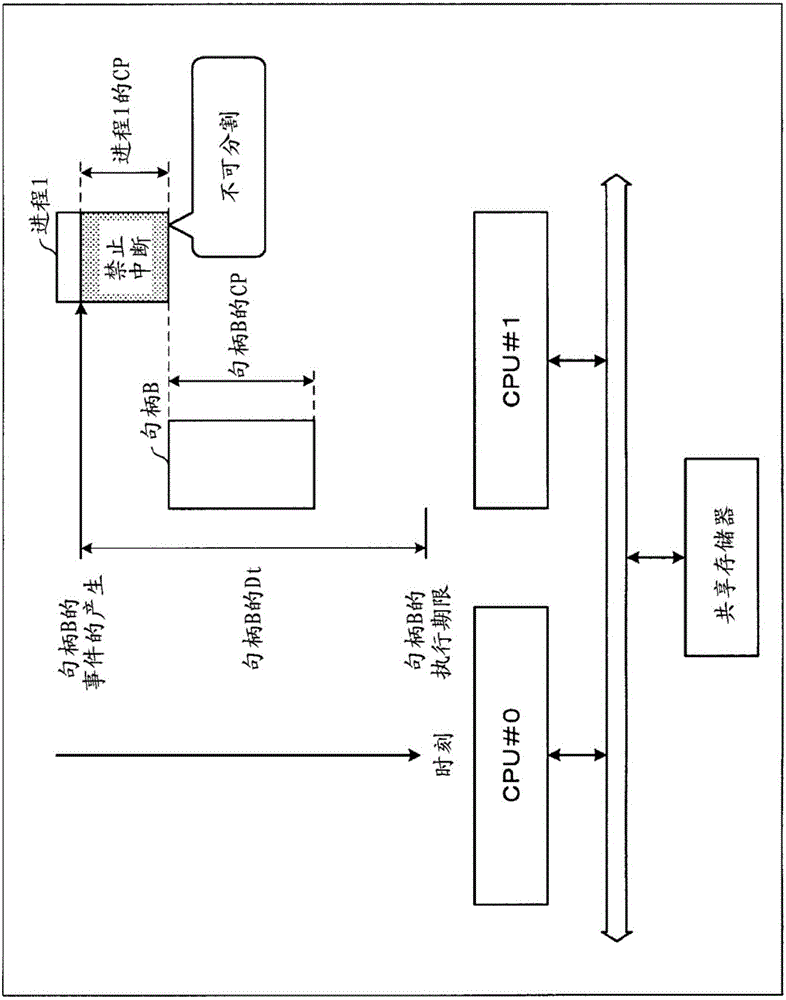

[0050] In Embodiment 1, the calculation of the execution time of each driver will be described using the ESL (Electronic System Level) model. Here, the ESL model refers to a technique for simulating a hardware environment by describing based on the behavior (behavior) of a hardware device. For example, in the ESL model of the CPU, the mechanism of the electrical circuit for issuing commands is not simulated as it is, but is represented by issuing commands and the time required for them.

[0051] In addition, in the ESL model of the bus, the circuit mechanism is not used to strictly calculate the delay of data propagation, but the latent mode of the design is multiplied according to the access requirements, and the concept of action and time is used as behavior (action) to simulate.

[0052] Conventionally, simulation refers to performing simulation without actually mounting semiconductors based on circuit design information such as RTL (Register Transfer Level), and is used fo...

Embodiment approach 2

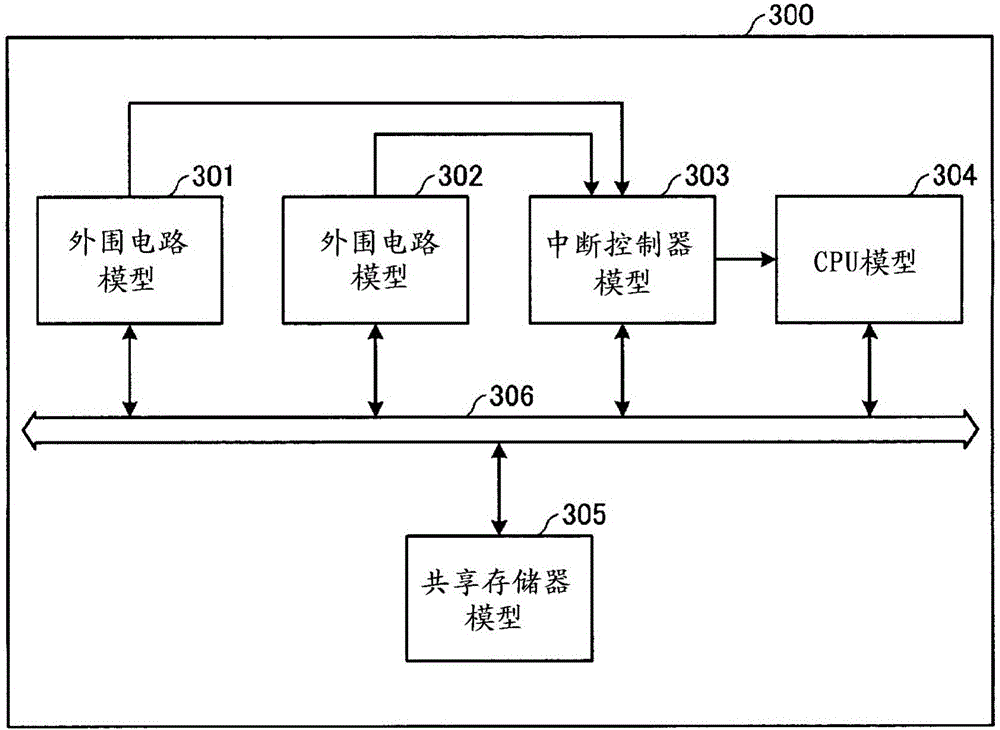

[0085] Next, in Embodiment 2, distribution of drivers and distribution of applications will be described. Here, in a multi-core processor system, a multi-core processor refers to a processor equipped with a plurality of cores. As long as it is equipped with multiple cores, it may be a single processor equipped with multiple cores, or a processor group in which single-core processors are paralleled. In this embodiment, in order to simplify the description, a processor group in which single-core processors are arranged in parallel is used as an example for description.

[0086] (hardware for multi-core processor systems)

[0087] Figure 9 is a block diagram representing the hardware of a multi-core processor system. The multi-core processor system 900 includes a peripheral circuit 901 , a peripheral circuit 902 , an interrupt controller 903 , CPU#0 , CPU#1 , a shared memory 905 , and a clock supply circuit 906 . Each part is connected by the bus 904 .

[0088] CPU#0 and CP...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com