Resistance voltage divider type DAC-PUF circuit

A resistance divider and resistance technology, applied in logic circuits, electrical components, digital-to-analog converters, etc., can solve the problems of large resistance deviation range and deviation of actual resistance value from theoretical value, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

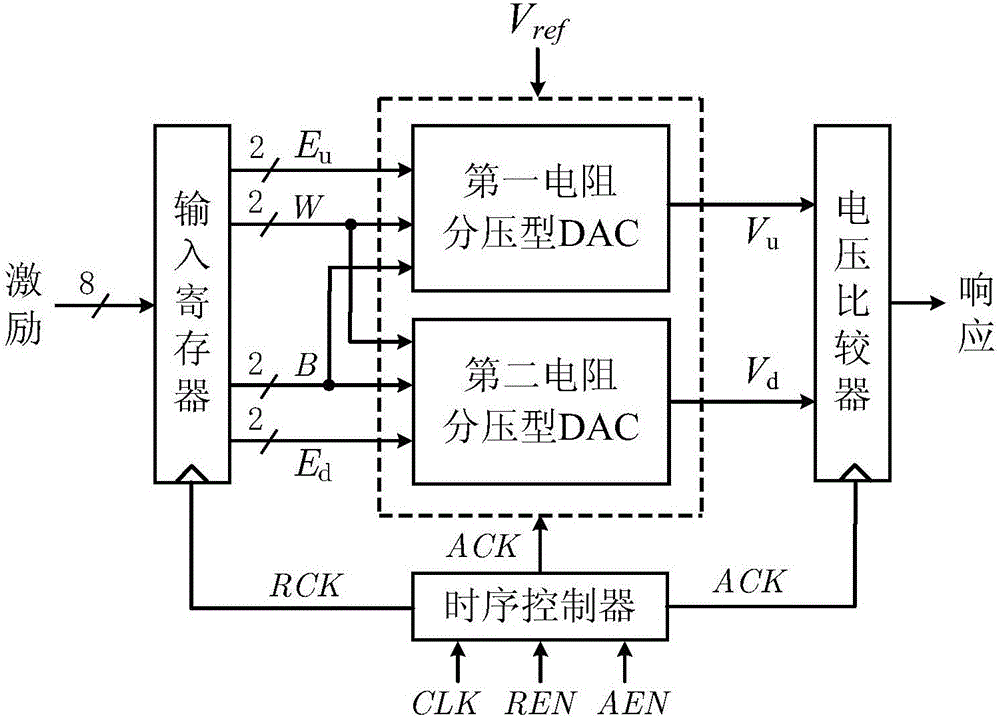

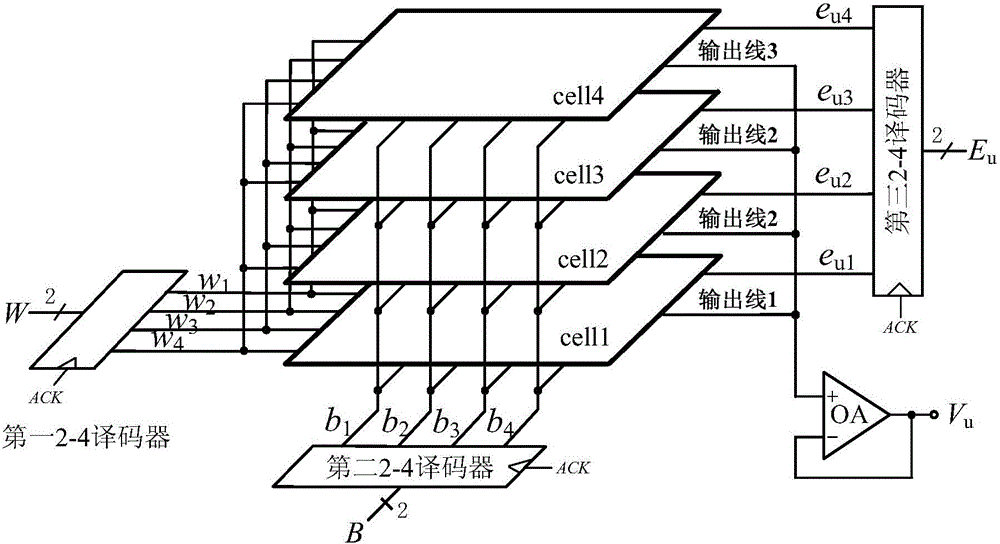

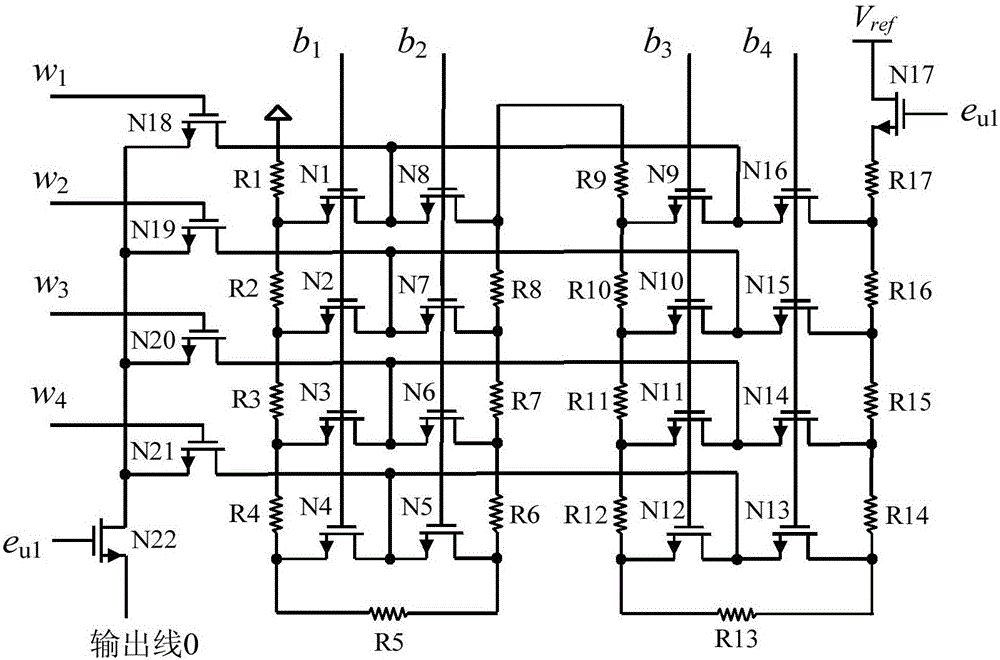

[0022] Embodiment one: if Figure 1 ~ Figure 3As shown, a resistor divider DAC-PUF circuit includes an input register, an offset voltage generating circuit, a voltage comparator and a timing controller. The input register has a clock terminal, an input terminal, a first output terminal, a second output terminal, The third output terminal and the fourth output terminal, the voltage comparator has a clock terminal, a first input terminal, a second input terminal and an output terminal, the timing controller is respectively connected to the clock terminal of the input register and the clock terminal of the voltage comparator, and the deviation The voltage generating circuit includes two resistor divider DACs with the same structure, and the resistor divider DAC includes three 2-4 decoders with the same structure, operational amplifiers and four resistor divider units with the same structure, and the 2-4 translator The coder has a clock terminal, an input terminal, a first output ...

Embodiment 2

[0023] Embodiment two: if Figure 1 ~ Figure 3As shown, a resistor divider DAC-PUF circuit includes an input register, an offset voltage generating circuit, a voltage comparator and a timing controller. The input register has a clock terminal, an input terminal, a first output terminal, a second output terminal, The third output terminal and the fourth output terminal, the voltage comparator has a clock terminal, a first input terminal, a second input terminal and an output terminal, the timing controller is respectively connected to the clock terminal of the input register and the clock terminal of the voltage comparator, and the deviation The voltage generating circuit includes two resistor divider DACs with the same structure, and the resistor divider DAC includes three 2-4 decoders with the same structure, operational amplifiers and four resistor divider units with the same structure, and the 2-4 translator The coder has a clock terminal, an input terminal, a first output ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More