Anti-single-event transient reinforcement SOI member and manufacture method for the same

An anti-single event and transient technology, applied in the field of microelectronics, can solve the problems of SiGe junction depth and difficulty in controlling, and achieve the effects of suppressing single event transient effects, suppressing amplification, and reducing potential

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The present invention will be further described in conjunction with the accompanying drawings and specific embodiments.

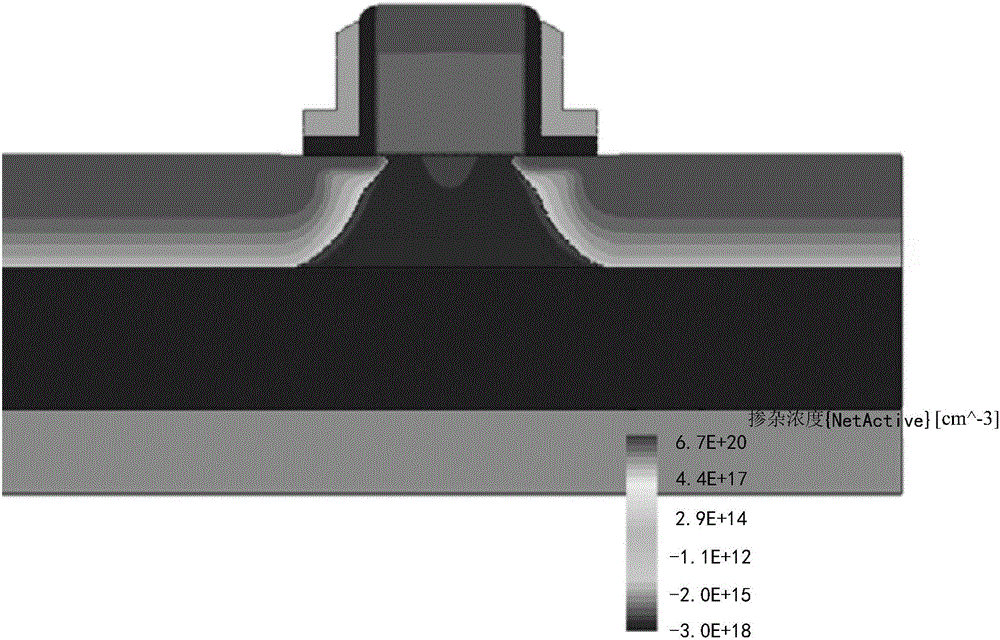

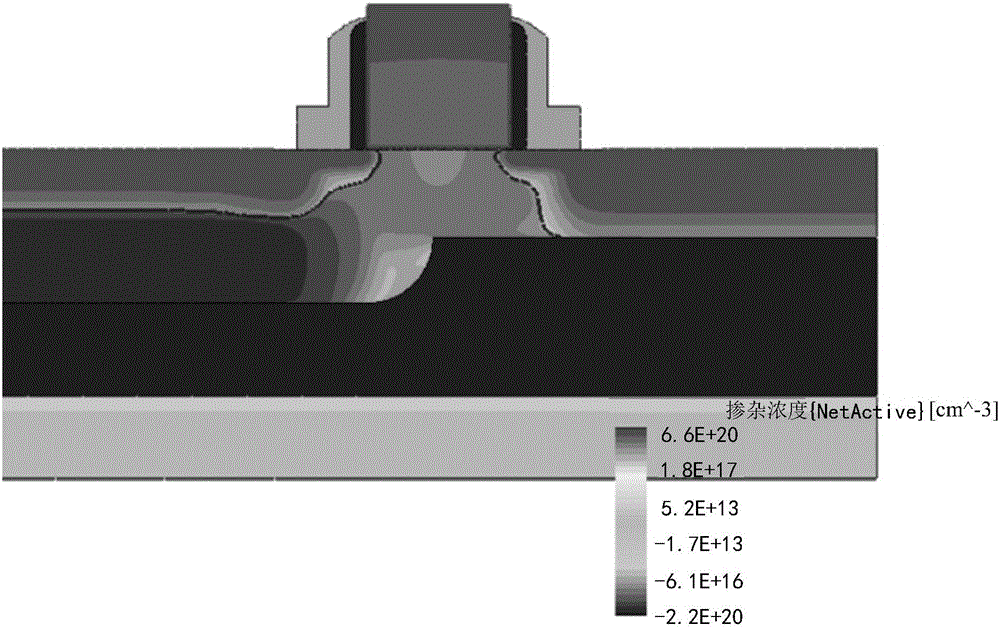

[0030] Such as Figure 7 As shown, an anti-single event transient hardened SOI device includes a substrate 1, a buried oxide layer 2, a semiconductor body region 3, a drain region 9, a source region 10, a gate region, a gate spacer 11, an LDD region 7 and a heavy The doped source extension region 8, the buried oxide layer 2 is located on the substrate 1, the material of the buried oxide layer 2 is silicon dioxide, and the semiconductor body region 3, the source region 10 and the drain region 9 are located between the buried oxide layer 2 , and the semiconductor body region 3 is located between the source region 10 and the drain region 9, the LDD region 7 is located at the top of both sides of the semiconductor body region 3 and is in contact with the source region 10 and the drain region 9 respectively, and the gate region is located at the top of th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More