Internal gate type MOS

A gate type, epitaxial layer technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of large cell size of NexFET structure, complex manufacturing process, large chip area, etc., to solve the problem of on-resistance and high withstand voltage , The effect of reducing gate-drain capacitance Cgd and reducing Rdson

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

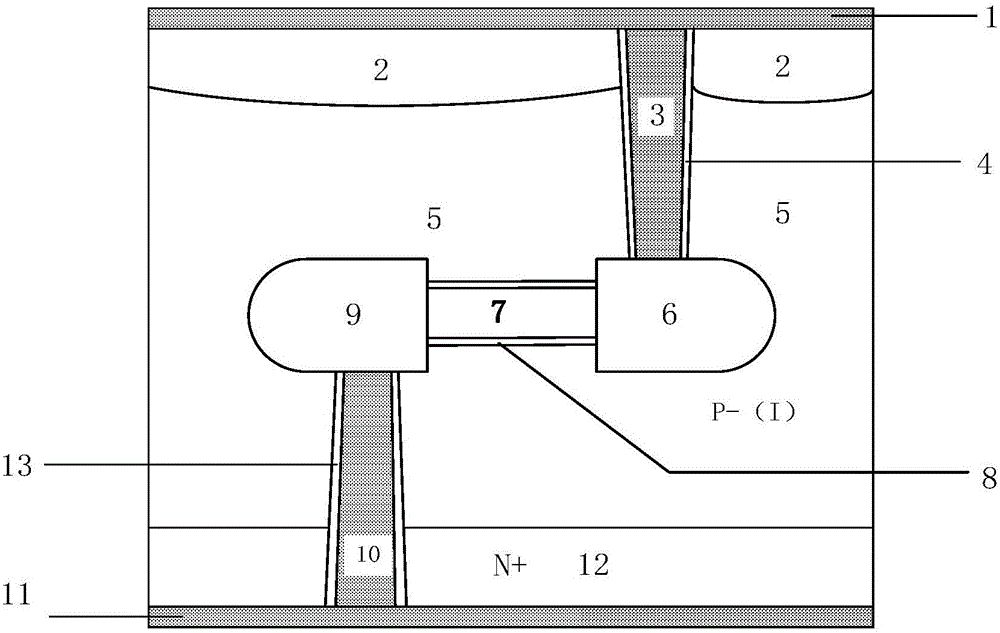

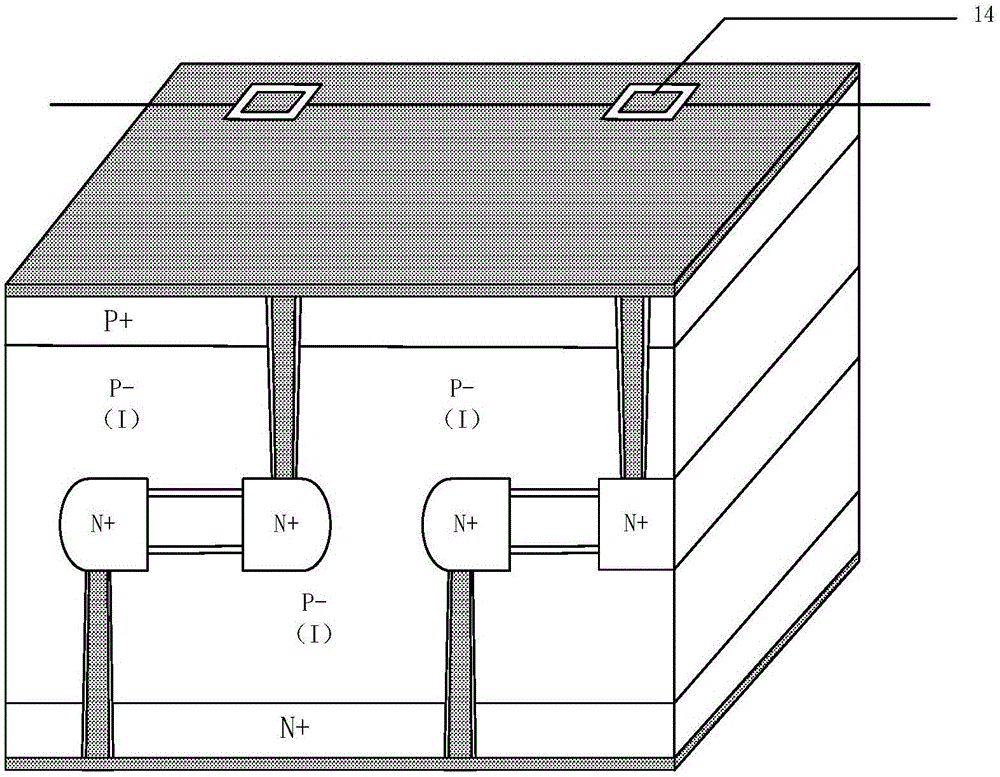

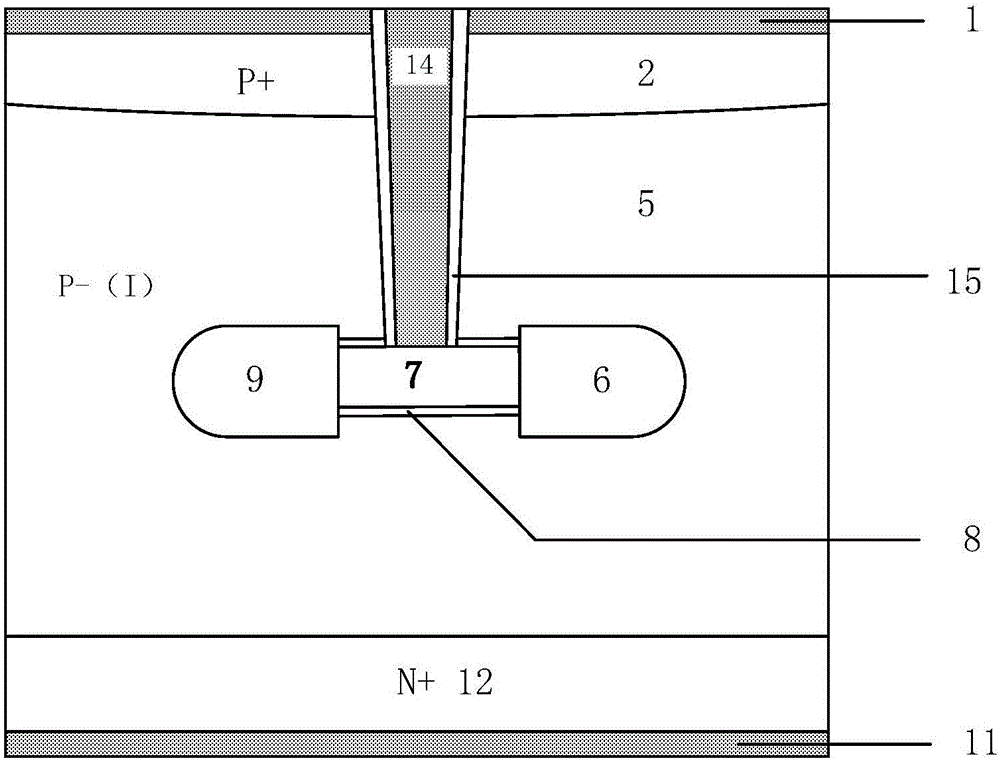

[0026] Describe technical scheme of the present invention in detail below in conjunction with accompanying drawing

[0027] Such as figure 1 As shown, an internal gate MOS of the present invention includes a drain electrode 11, an N-type heavily doped single crystal silicon substrate 12, a low-doped P-type epitaxial layer 5, a highly doped P+ source region 2 and source metal electrode 1; the doped P-type epitaxial layer 5 has a strip-shaped source region 6 and a strip-shaped drain region 9, and the strip-shaped source region 6 and strip-shaped drain region 9 are located on the same horizontal plane , and the strip-shaped source region 6 and the strip-shaped drain region 9 are connected by a polysilicon gate 7, and the polysilicon gate 7 is isolated from the low-doped P-type epitaxial layer 5 by a gate oxide layer 8; the strip-shaped source region 6 is connected by The first deep groove metal 3 that runs through the highly doped P+ source region 2 is connected to the source me...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More