Signed probability calculating unit based on probability Turbo decoder

A probability calculation and decoder technology, applied in the field of decoding algorithms, can solve the problems of low precision, high complexity and slow convergence of computing units, and achieve the effect of overcoming the low precision of computing units

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

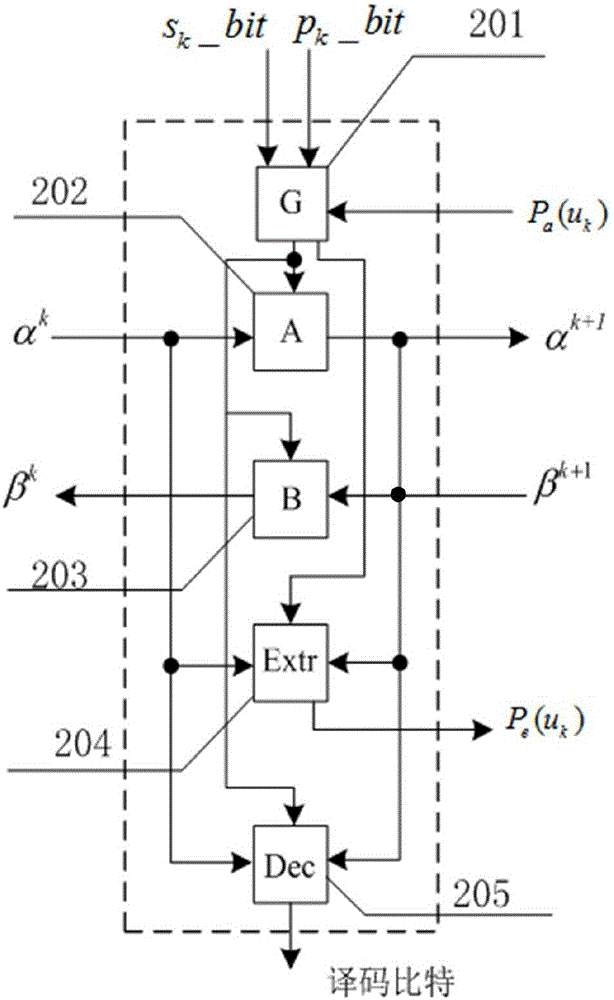

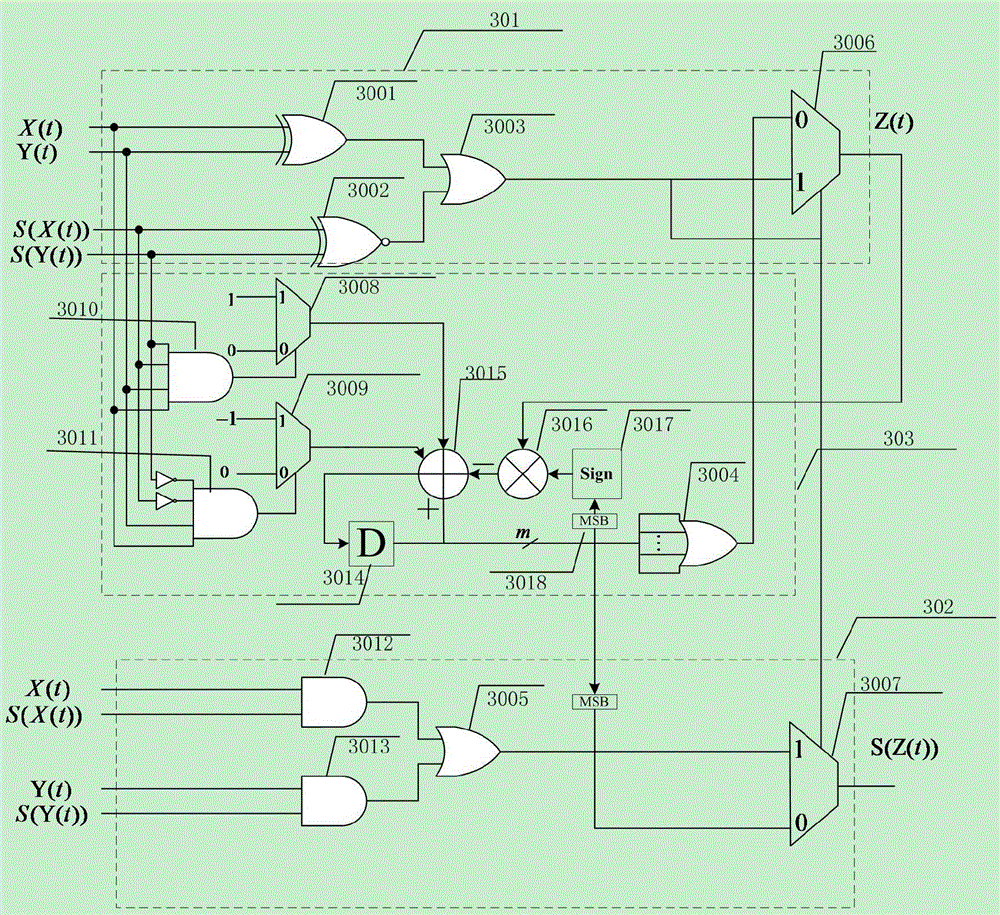

[0055] For the probability turbo decoder based on Log-MAP, the present invention provides a probability calculation unit based on the probability turbo decoder, the probability adder in the probability calculation unit includes a random bit calculation module 301, a sign bit calculation module 302 And a saturation carry storage update module 303;

[0056] The random bit calculation module 301, the sign bit calculation module 302 and the saturation carry storage update module 303 are connected any two;

[0057] The random bit calculation module 301 completes the random bit calculation;

[0058] The sign bit calculation module 302 completes the sign bit calculation;

[0059] The saturated carry storage update module 303 realizes the storage update of the saturated carry.

[0060] Further, the random bit calculation module 301 includes an exclusive OR gate 3001, an exclusive OR gate 3002, a first OR gate 3003 and a first multiplexer 3006;

[0061] The XOR gate 3001 inputs the ...

Embodiment 2

[0085] The probability calculation unit described in embodiment 2 also includes a probability normalization unit, Figure 5 The implementation structure of the 8-input probability normalization unit in the forward state metric calculation module 202 and the backward state metric calculation module 203 is given. Further, the probability normalization unit in the probability calculation unit includes an input module 401, a second full adder 402, a second register 403, a fourth OR gate 404, a fifth OR gate 405, an input judgment module 410 and a TFM module 420;

[0086] The input module 401, the second full adder 402, the second register 403 and the fourth OR gate 404 are sequentially connected;

[0087] The second register 403 stores a saturated carry result, and the fourth OR gate 404 realizes a function of judging whether the saturated carry result is greater than 0;

[0088] The input judging module 410 is connected to the input module 401, which includes a sixth gate 406 w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More