High-speed variable point FFT (Fast Fourier Transform) processor based on FPGA (Field-Programmable Gate Array) and processing method of high-speed variable point FFT processor

A processor and variable technology, applied in the direction of complex mathematical operations, etc., can solve the problems of low portability of modules, complex control logic of FFT processors, etc., to overcome complex addressing, multiple processing cycles, and high accuracy of data results Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] The FFT processor of the present invention will be further described below in conjunction with the accompanying drawings.

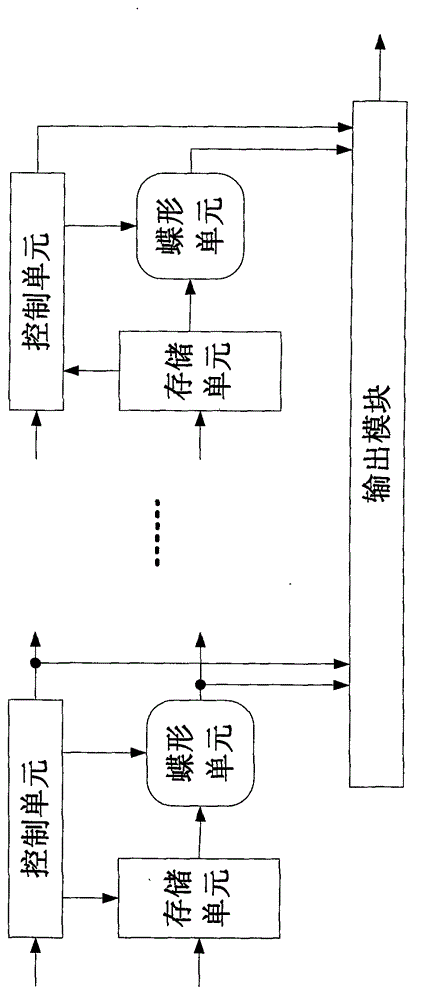

[0038] Refer to attached figure 1 , the variable-point pipeline FFT processor of the present invention includes a multi-stage processing module and an output module, and the multi-stage processing module and the output module are cascaded in a pipeline mode; the storage unit, the control unit and the butterfly unit in the processing module pass data The bus is connected to the control bus; the total cascade number of the multistage processing module is determined by the maximum length of the sequence of the FFT operation performed by the user (the sequence length is an integer power of 2), and the total number of stages of the processing module is 10 in the present embodiment, which can be The longest data sequence to be processed is 1024 points, and the FFT operation processing of 2 to 1024 points can be realized by setting the series of processin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More