Multi-chip joint simulation method based on traditional EDA tool

A co-simulation, multi-chip technology, used in design optimization/simulation, CAD circuit design, special data processing applications, etc., can solve problems such as abnormal circuit operation, avoid manual misoperation, improve reusability, and improve simulation. The effect of efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The embodiments listed in the present invention are only used to help understand the present invention, and should not be interpreted as limiting the protection scope of the present invention. For those of ordinary skill in the art, they can also Improvements and modifications are made to the present invention, and these improvements and modifications also fall within the protection scope of the claims of the present invention.

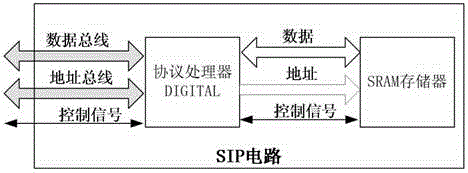

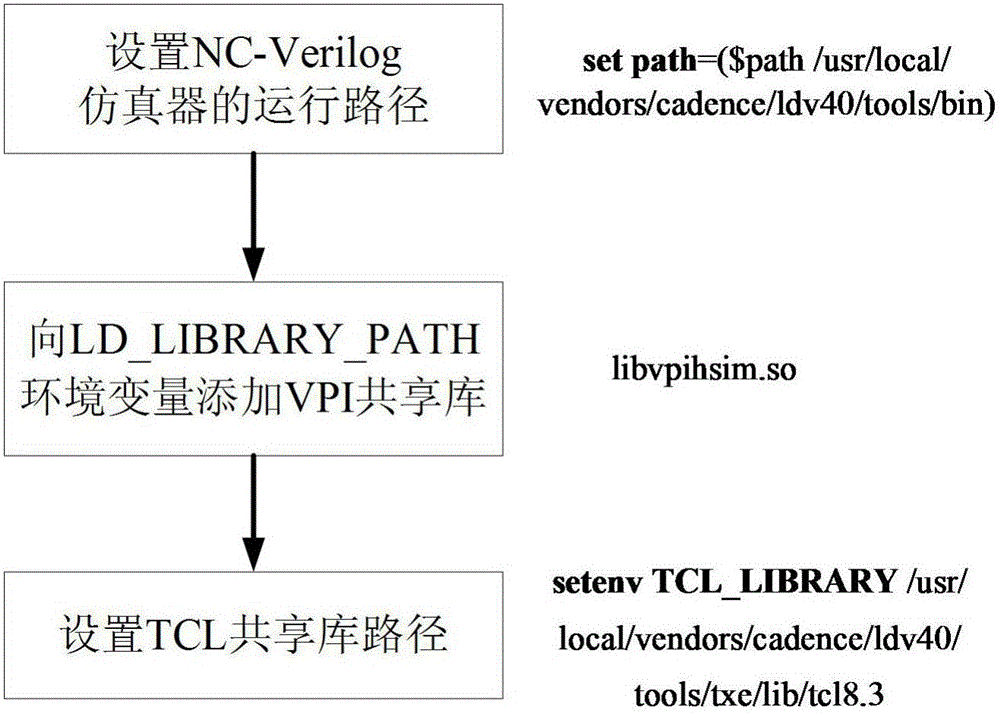

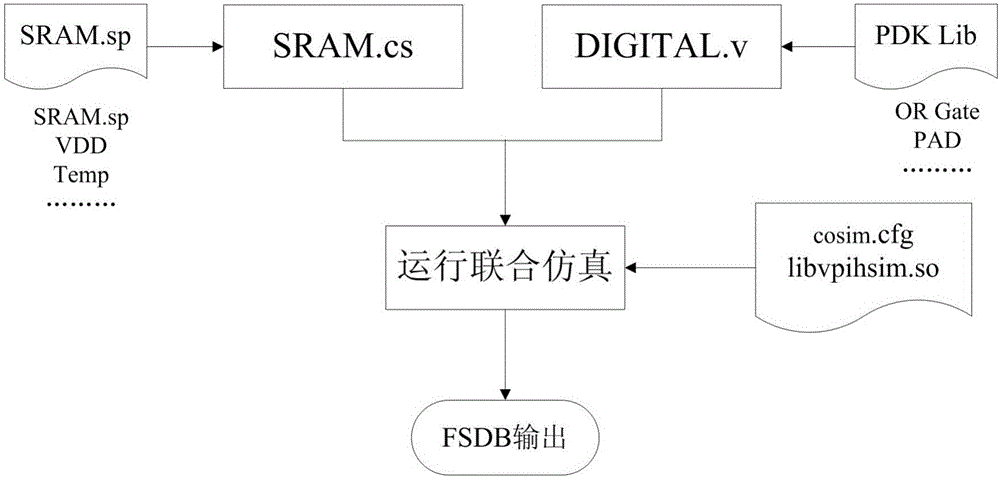

[0022] The present invention is introduced with a SiP circuit composed of protocol processor DIGITAL (digital logic subcircuit) and SRAM memory (analog subcircuit). The composition structure of SiP circuit is as attached figure 1 shown. The simulation tool that the present invention needs is the Verilog simulator NC-Verilog of Cadence Company and the Spice simulator HSIM of Synopsys Company. During co-simulation, the system will call Verilog Program Interface (VPI) or Programmable Language Interface (PLI) to interact with HSIM and NC-Verilog ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More