Wafer flattening method

A flattening method and wafer technology, applied in gaseous chemical plating, decorative art, microstructure technology, etc., can solve problems such as wafer surface collapse, achieve the effects of reducing removal, controlling collapse, and increasing removal

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

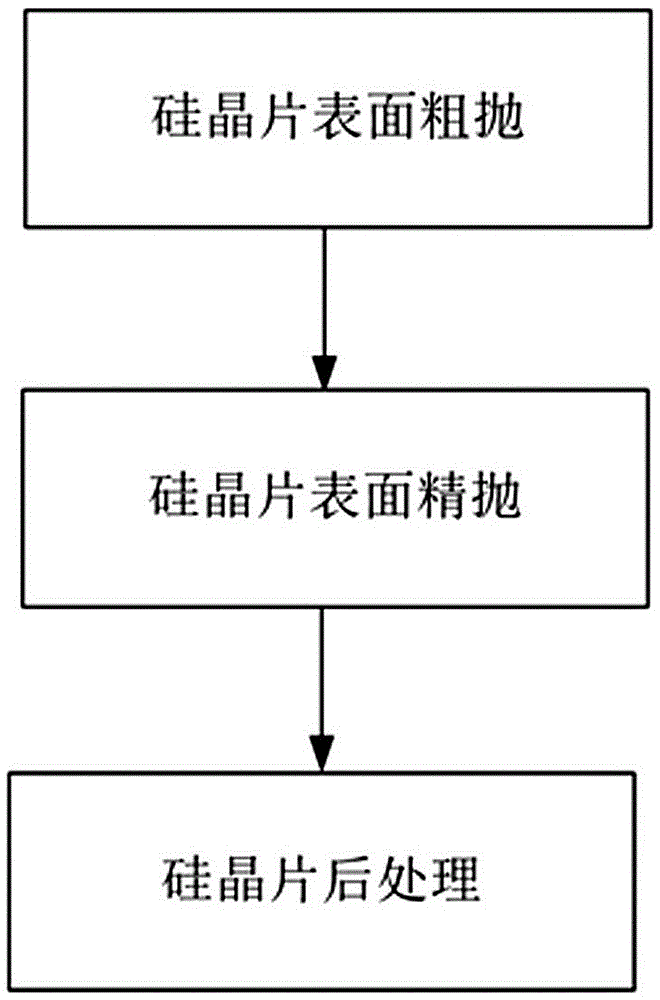

[0033] Hereinafter, embodiments of the wafer planarization method of the present invention will be described with reference to the accompanying drawings.

[0034] The examples described here are specific specific implementations of the present invention, and are used to illustrate the concept of the present invention. They are all explanatory and exemplary, and should not be construed as limiting the implementation of the present invention and the scope of the present invention. In addition to the embodiments described here, those skilled in the art can also adopt other obvious technical solutions based on the claims of the application and the contents disclosed in the description, and these technical solutions include adopting any obvious changes made to the embodiments described here. Replacement and modified technical solutions.

[0035] The accompanying drawings in this specification are schematic diagrams, which assist in explaining the concept of the present invention, a...

PUM

| Property | Measurement | Unit |

|---|---|---|

| particle diameter | aaaaa | aaaaa |

| compression ratio | aaaaa | aaaaa |

| hardness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More