Circuit for loading FPGA configuration file through serial port

A configuration file and circuit technology, applied in electrical digital data processing, instruments, etc., can solve the problems of inability to easily expand the programming method and high cost, and achieve the effect of high price, small capacity, and reduced hardware cost.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

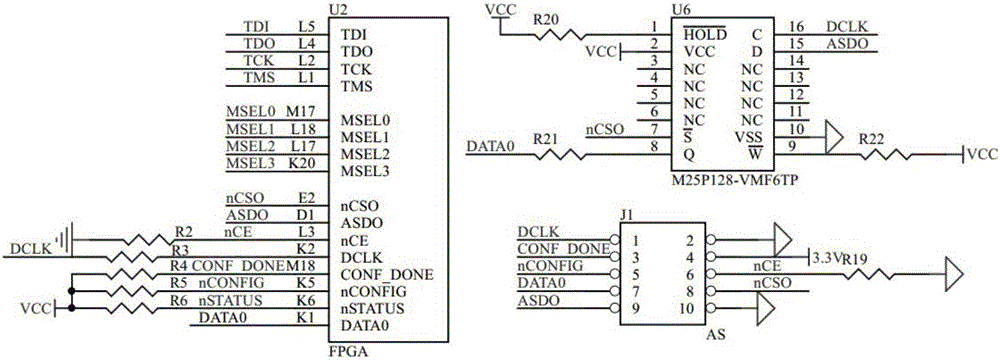

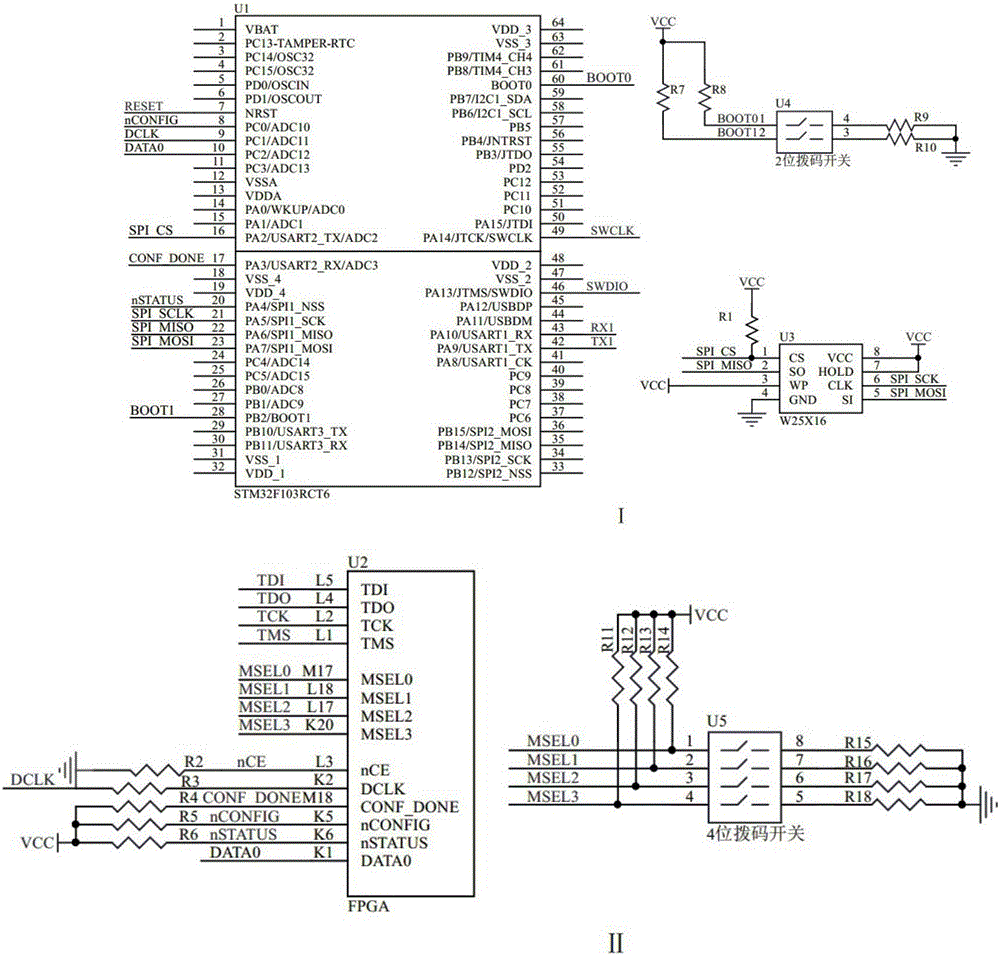

[0015] Such as figure 2 As shown, the invention discloses a circuit for loading an FPGA configuration file through a serial port, including a single-chip circuit I and an FPGA circuit II. The circuit includes 1 single-chip microcomputer chip, 1 FPGA chip, 1 FLASH chip, and 18 chip resistors. The microcontroller chip U1 is STM32F103RCT6, the flash chip U3 is W25X16, U4 is a two-position DIP switch, U5 is a four-position DIP switch, resistors R7 and R8 are 510Ω, and resistors R1, R9 and R10 are 10KΩ.

[0016] The MCU circuit includes a two-position DIP switch, a W25X16 chip and a STM32F103RCT6 chip, and five resistors R1, R7, R8, R9, R10; pin 60 of the chip U1 is connected to pin 1 of the DIP switch U4, and the chip U1 The 28th pin of the DIP switch U4 is connected to the 2nd pin of the DIP switch; one end of the resistor R7 is connected to 3.3V, and the other end of the resistor R7 is connected to the 2nd corner of the DIP switch U4; one end of the resistor R8 is connected to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com