High-frequency clock frequency detection structure for resisting attack chip

A high-frequency clock and frequency detection technology, applied in the monitoring of pulse chain mode, platform integrity maintenance, etc., to achieve the effects of insensitivity to process errors, reduced system power consumption, and small layout area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

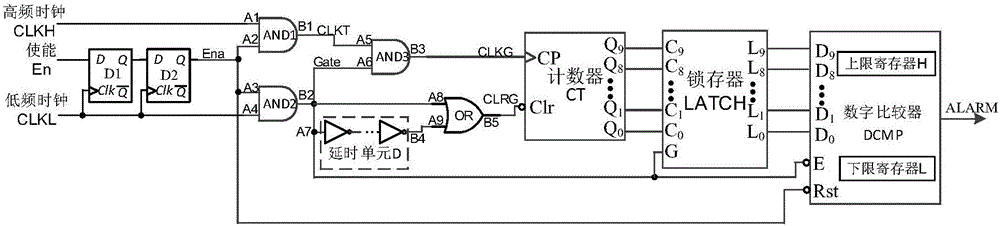

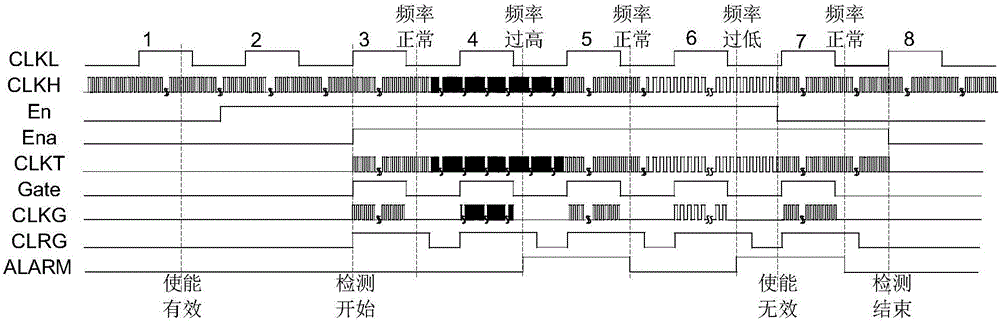

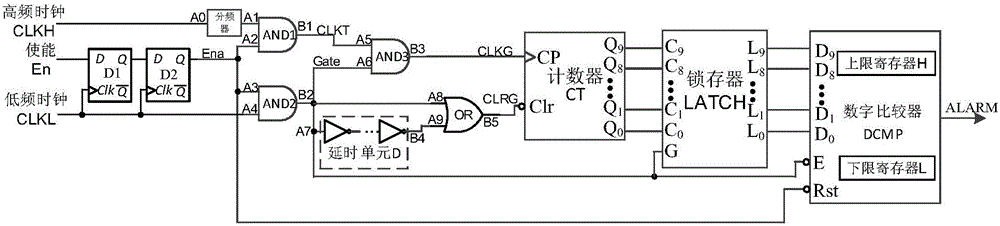

[0021] The technical solution of the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments, and the described specific embodiments are only for explaining the present invention, and are not intended to limit the present invention.

[0022] Aiming at the problem that anti-attack chips are vulnerable to frequency attacks, the present invention proposes a frequency measurement circuit for externally input high-frequency clocks. The circuit effectively uses the internal low-frequency clock as a counting gate to count the number of high-frequency clock cycles within a fixed time , thus pushing the high-frequency clock frequency. When the obtained frequency exceeds the normal operating frequency range, an alarm signal is generated.

[0023] A kind of high-frequency clock frequency detection structural circuit for the anti-attack chip proposed by the present invention, a technical scheme of its implementatio...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More