A PD-PWM Modulation Method Based on Dynamic Carrier Offset Allocation

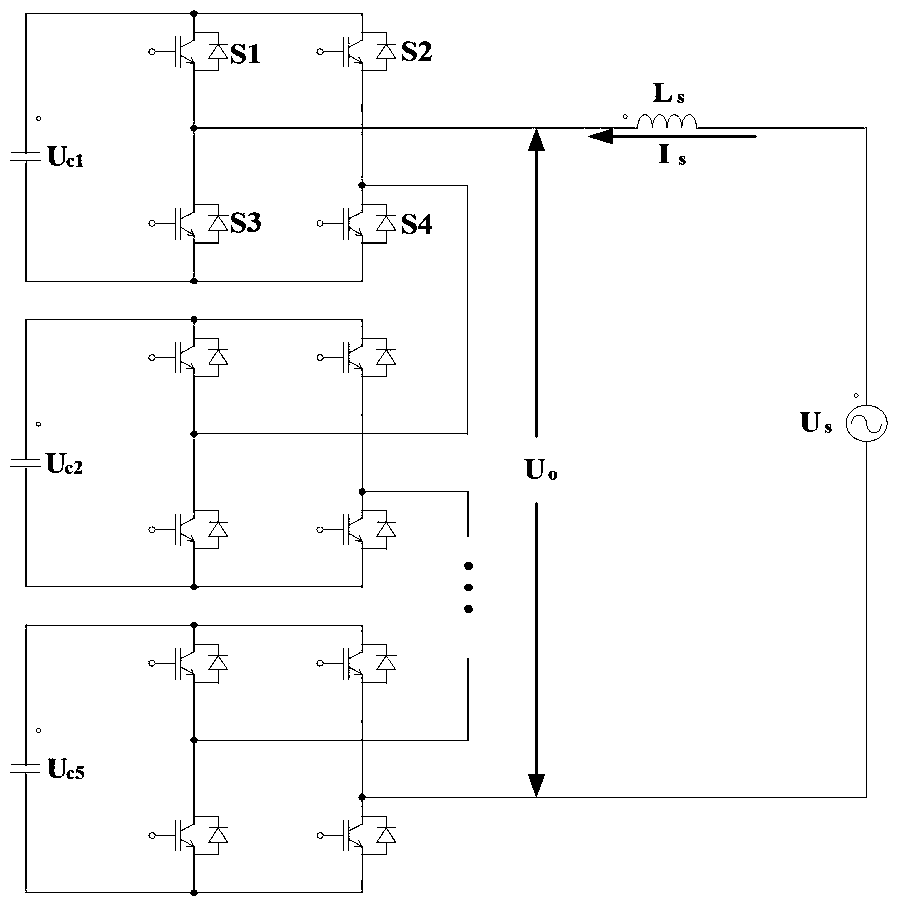

A technology of PD-PWM and modulation method, which is applied to output power conversion devices, electrical components, and AC power input to DC power output. Improve stability, fast error correction ability, and have the effect of error tolerance mechanism

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

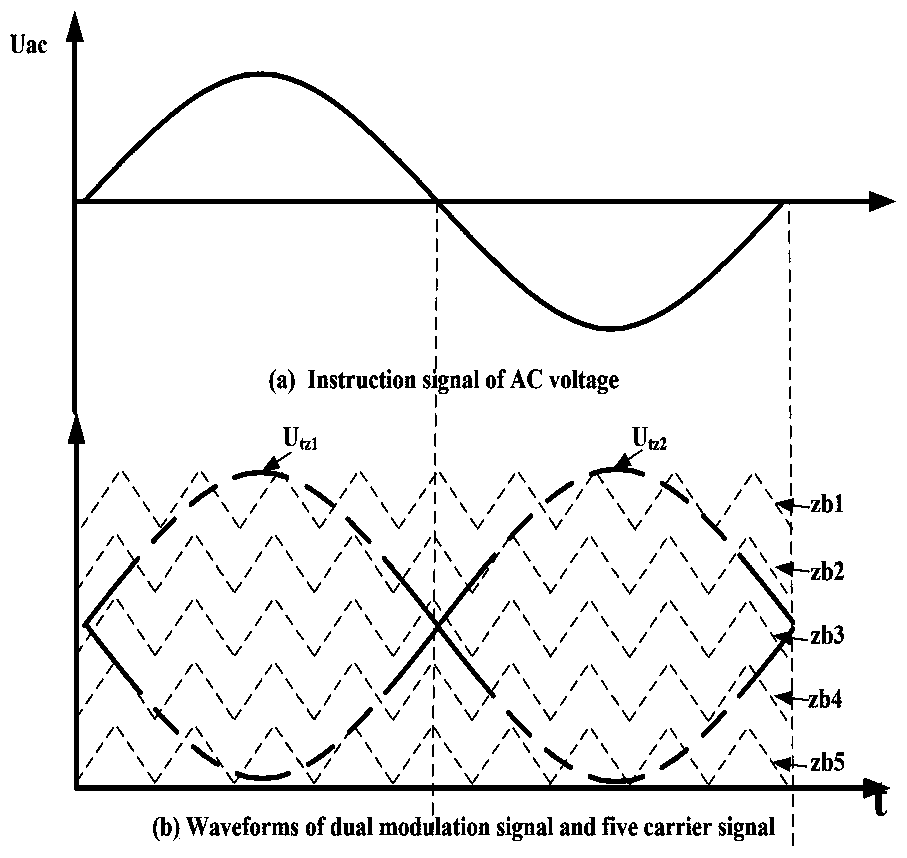

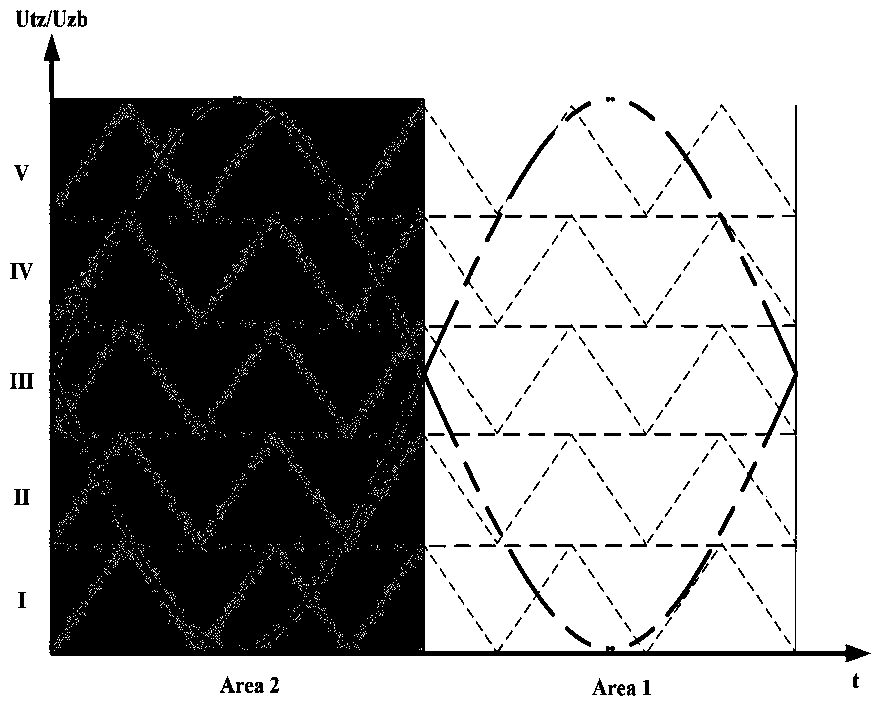

Method used

Image

Examples

Embodiment

[0058] The present invention builds a single-phase inverter model of the CHB grid-connected model in the electromagnetic transient simulation software PSIM, and the simulation parameters are shown in Table 4.

[0059] Table 4 Simulation parameters

[0060] parameter name

parameter value

100V

[0061] rated value

Number of subunits

5

10mF

Grid-connected inductance

10mH

AC voltage frequency

50Hz

[0062] 1. Compared with the traditional cyclic carrier offset distribution type PD-PWM

[0063] In order to test the dynamic voltage equalization characteristics of the method of the present invention, and compare it with the traditional cyclic conversion carrier bias type PD-PWM, the present invention has carried out the following simulation: the system first selects the DC bus capacitance parameters of the subunits to be consistent, and adopts Cycli...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More