On-chip parallel SerDes system and implementation method

A technology of parallelizer and system clock, which is applied in the system field of on-chip SerDes technology, can solve the problems of insufficient GPU bandwidth, achieve high storage bandwidth, improve data bandwidth, and save wiring space resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

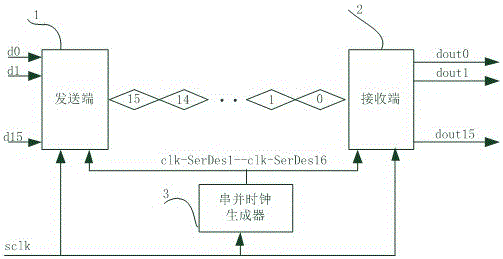

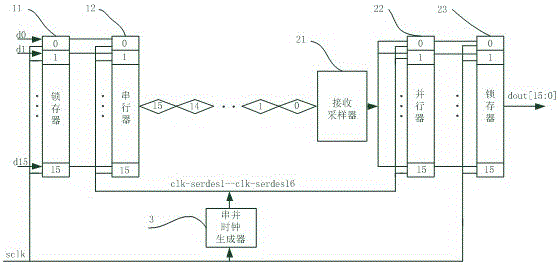

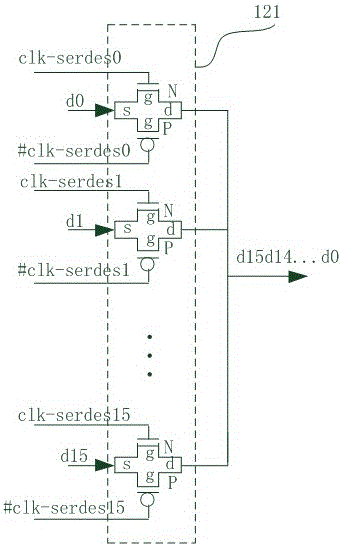

[0029] like figure 1 As shown, a top-level topology diagram of an on-chip parallel SerDes system of the present invention. Including: data sending end 1, complete data parallel to serial conversion; data receiving end 2, complete data serial conversion to parallel; serial parallel clock generator 3, generate 16-phase clock clk- SerDes1--clk-SerDes16. Wherein, the data sending end 1 converts the input 16-bit parallel data d15-d0 into serial data d0, d1, . . . , d15 under the control of the system clock sclk, and sends them out. Send d0 first, then d1, and finally d15. The data receiver 2 converts the received serial data d0, d1,...,d15 into parallel data d15-d0 under the control of the system clock sclk, and then sends them out. The system clock sclk is responsible for the clock synchronization of the sending end and the receiving ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More