Block-floating-point method for FFT (fast Fourier transform) processor

A block floating point and processor technology, which is used in electrical digital data processing, digital data processing components, instruments, etc., and can solve problems such as the inability to support FFT processors with adjustable data block sizes.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

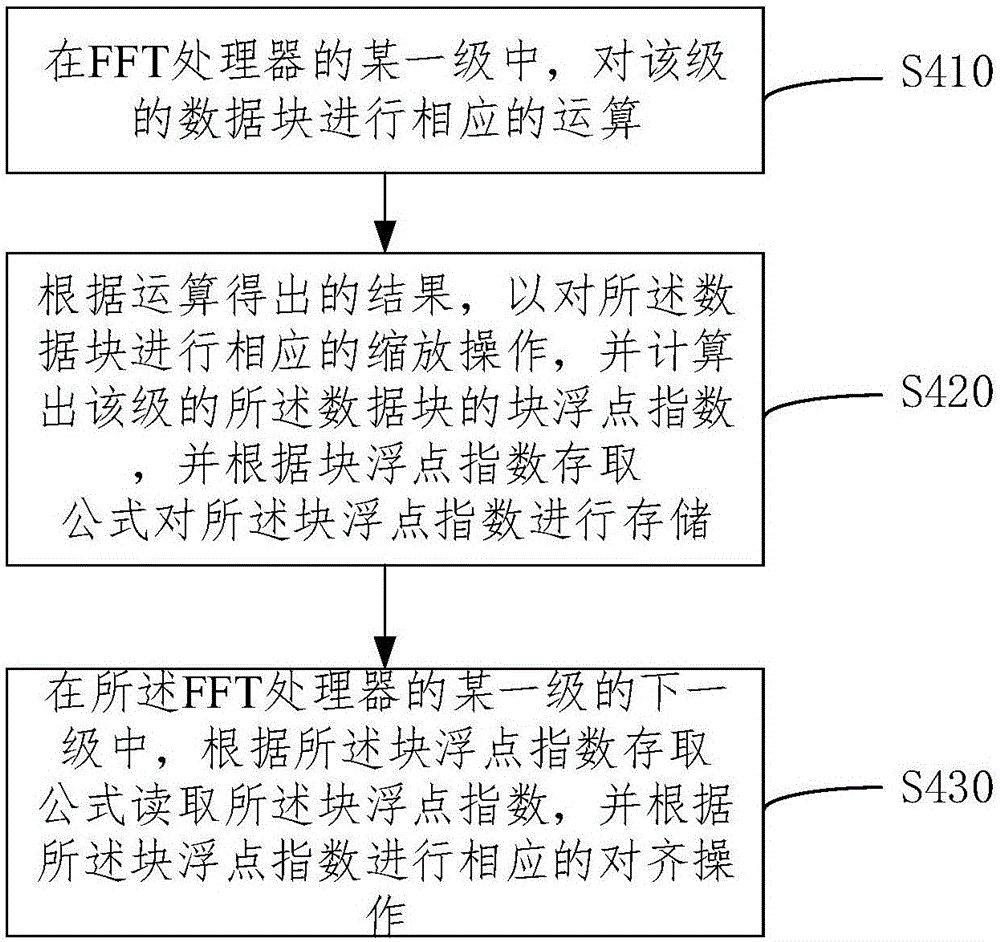

Method used

Image

Examples

Embodiment 1

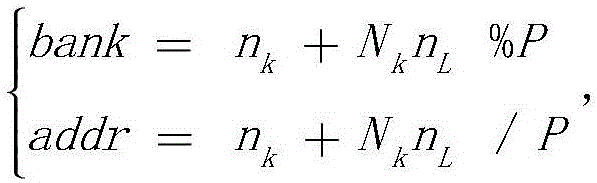

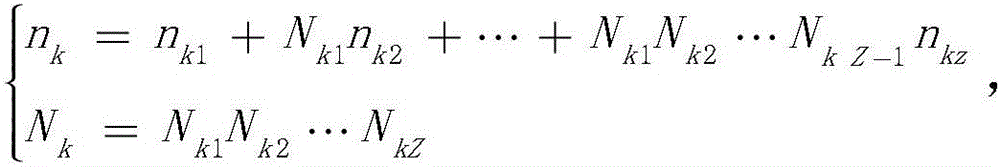

[0059] Assume that the maximum data parallelism P that the FFT processor can access in parallel is 16. And the FFT processor uses the mixed base algorithm to decompose the N-point FFT operation into m-level butterfly operations:

[0060] N = N 1 N 2 ... N m n = N m N m - 1 ... N 2 n 1 + ... + ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More