Method for time sequence analysis of digital circuit design and system for time sequence analysis of digital circuit design

A timing analysis and digital circuit technology, applied in the fields of electrical digital data processing, computing, special data processing applications, etc., it can solve the problems of unable to consider timing data, unable to read ETM, unable to fully analyze ETM timing data, etc., to reduce Quantity, the effect of increasing efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

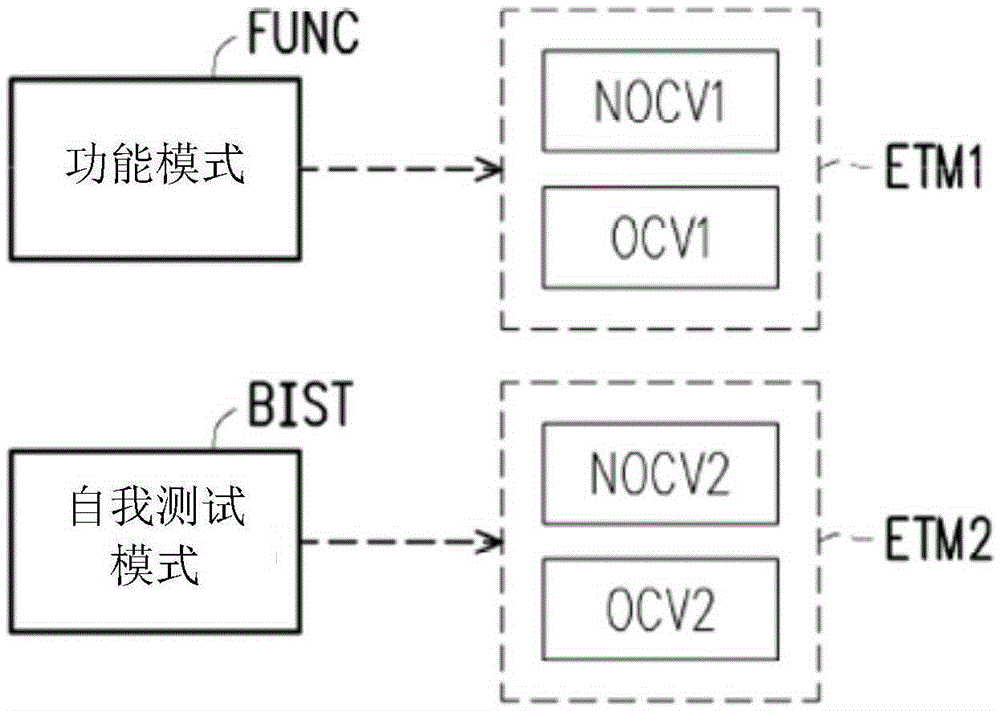

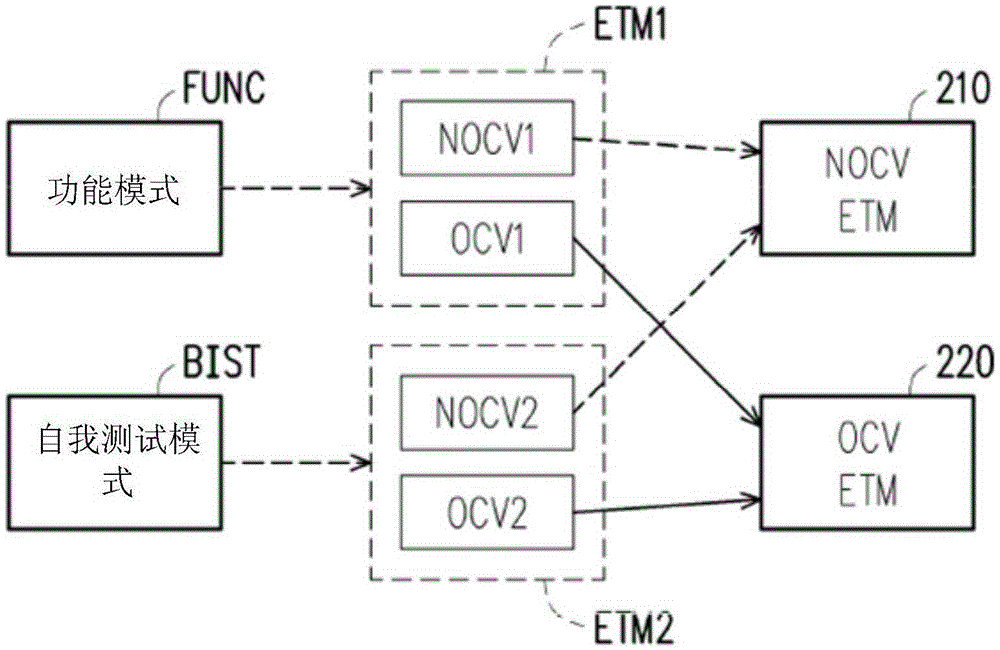

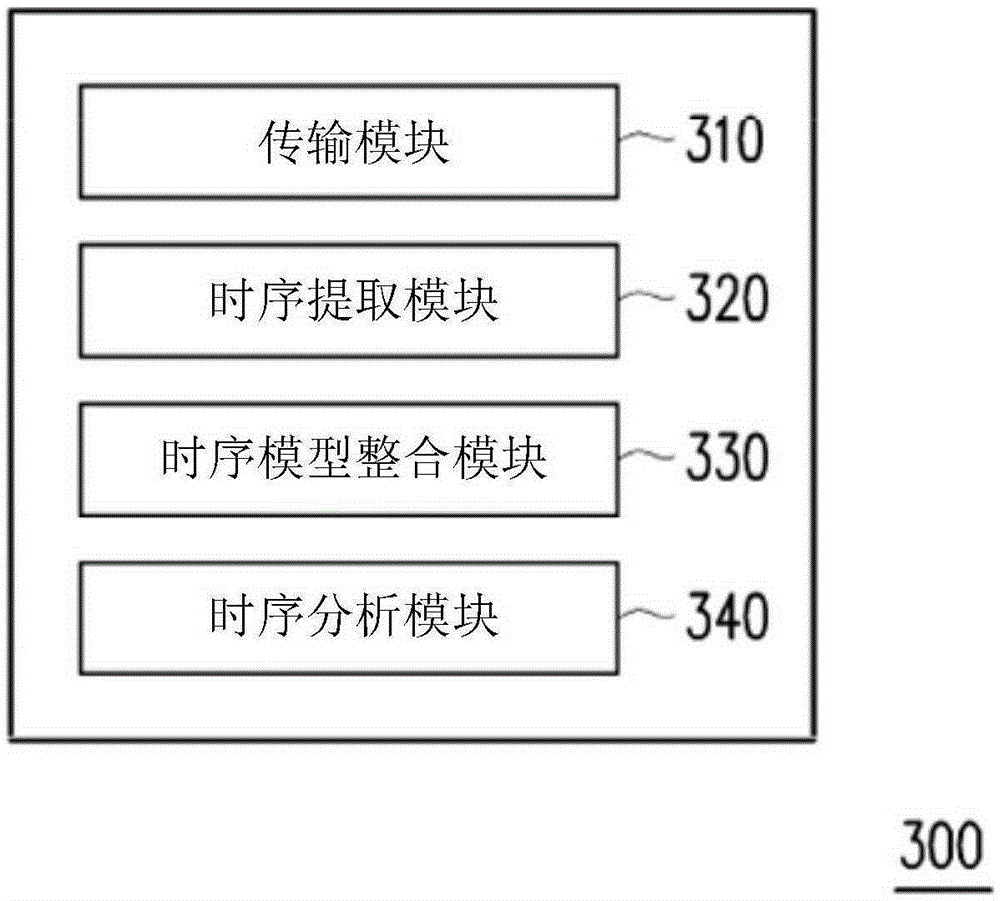

[0044] The extracted timing model (Extracted timing model, ETM for short) is a timing model and liberty file generated from the gate-level circuit diagram (netlist) of the chip. The ETM has the same timing behavior as the circuit diagram of the chip, and the data size of the ETM is much smaller than that of the circuit diagram, and the ETM can be used to replace the circuit diagram in hierarchical timing analysis. The arc delay of the ETM has various arc types in the ETM, and these arc delays vary with the input transition and output load of the circuit diagram. ETM is based on the circuit diagram of the block and the third-party program library (third (3) by using the STA analysis tool. rd ) party library) and other limitations, where the STA analysis tool only extracts the timing of the interface logic. In general, circuit diagrams usually have sequential circuits and combinational circuits. For ETM, sequential circuits have timing checking (e.g., setup, hold, clock gate) ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com