UVM based CAN controller IP verifying platform

A CAN controller and verification platform technology, applied in general control systems, control/regulation systems, CAD circuit design, etc., to achieve high efficiency, facilitate coverage statistics, and avoid confusion in execution sequences.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The present invention will be further elaborated below in conjunction with the accompanying drawings and specific embodiments.

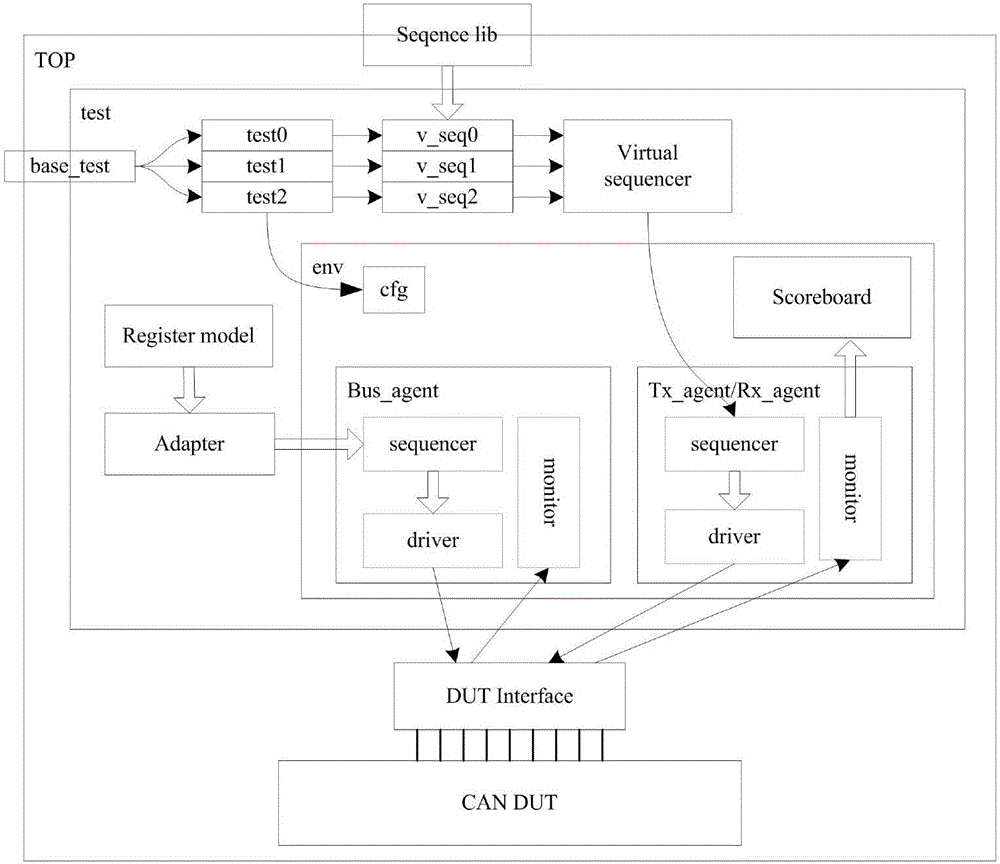

[0042] The architecture of the verification platform of the present invention is as follows: figure 2 As shown, the verification platform includes the top-level TOP layer, the design DUT under test, the DUT interface module interface, the test case layer test, the verification environment layer env, the register model register model, the virtual stimulus generator virtual seqencer, the register access agent bus_agent, and the sending end stimulus The sending and receiving agent tx_agent, the receiving end incentive sending and receiving agent rx_agent, the incentive generator sequencer, the incentive sending module driver, the interface monitoring module monitor, and the result comparison module scoreboard.

[0043] The TOP layer is the top layer of the verification platform, which instantiates the test case layer test of the CAN controller D...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More