Haar characteristic multi-processing framework human face detection system and method based on FPGA (Field Programmable Gate Array)

A face detection and multiprocessing technology, applied in instruments, character and pattern recognition, computer parts, etc., can solve the problems of slow processor operation speed and complex face feature detection algorithm.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

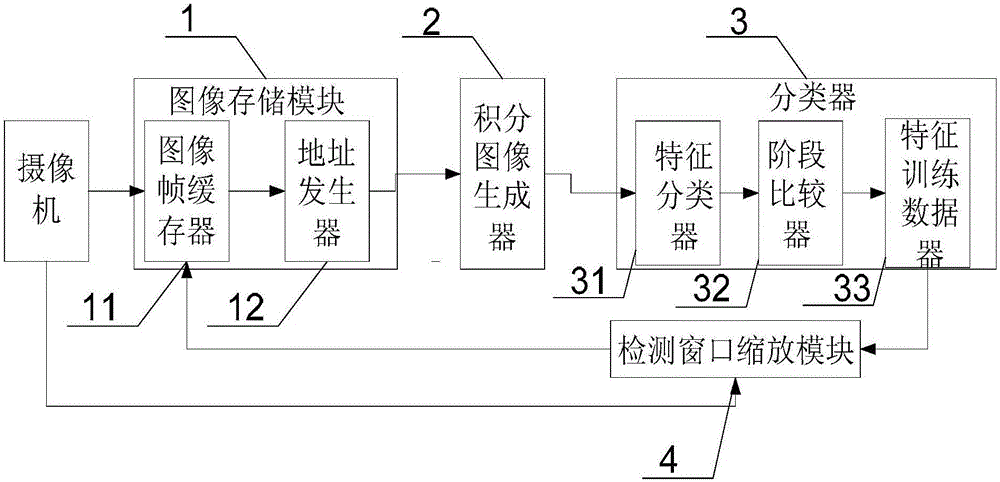

[0032] Specific implementation mode 1. Combination figure 1 Illustrate the present embodiment, the Haar feature multi-processing framework human face detection system based on FPGA described in the present embodiment, it comprises image storage module 1, integral image generator 2, classifier 3 and detection window scaling module 4;

[0033] The image storage module 1 is used to extract the haar feature in the range detection window of n×n in the camera acquisition image, utilize the haar feature to extract the face feature, and use the face feature to calculate the coordinates of each pixel point of the face feature; and calculate and obtain The coordinates of each pixel point of the face feature are sent out; where n is a positive integer;

[0034] Integral image generator 2 is used to receive each pixel point coordinates of facial features, utilizes integral map method according to each pixel point coordinates of facial features, calculates facial feature values; and sends ...

specific Embodiment approach 2

[0049] Specific embodiment two, this embodiment is a further description of the FPGA-based Haar feature multiprocessing architecture face detection system described in specific embodiment one, the image storage module 1 includes an image frame buffer 11 and an address generator 12,

[0050] The image frame buffer 11 is used to extract the haar feature in the range detection window of n × n in the camera acquisition image, utilizes the haar feature to extract the face feature; and sends the extracted face feature information;

[0051] Address generator 12 is used for receiving face feature information, and the face feature information that receives is stored as two-dimensional array, utilizes pixel address=(y*w+x), calculates the coordinate (x) of each pixel point of face feature , y), where w is the width of the integral map image, and sends out the coordinates of each pixel of the calculated facial features.

specific Embodiment approach 3

[0052] Specific embodiment three, this embodiment is a further description of the FPGA-based Haar feature multiprocessing architecture face detection system described in specific embodiment one, classifier 3 includes feature classifier 31, stage comparator 32 and feature training data Device 33;

[0053] The feature classifier 31 is used to receive and store the face feature value information, and compare the received face feature value P with the feature threshold A×m, and keep the face feature value P greater than the feature threshold A×m, which will be greater than the feature threshold value P The face feature value P of the threshold A×m is sent out; among them, m=1;

[0054] The stage comparator 32 is used to receive when m=2, the face feature value P greater than the feature threshold A × m, and use the received face feature value P to compare with the feature threshold A × m, and retain the face feature value P greater than the feature threshold A × m The face featur...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More