Alignment compensation system and method for lithographic apparatus

A technology of overlay compensation and photolithography, which is applied in the field of overlay compensation system to achieve the effect of high overlay accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] Specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

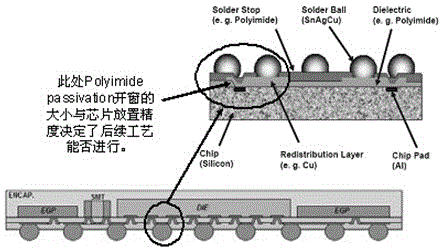

[0032] Figure 4 A lithographic apparatus that can be used to perform the steps of the method of the present invention is schematically shown, comprising: an illuminator 1, an illumination optical system for providing radiation; a mask table 3, for supporting a mask 2; a projection objective 4 , for imaging the pattern onto the reconstituted wafer 5 to be exposed; the workpiece table 6, used for fixing the reconstituted wafer 5 to be exposed; an overlay error measurement and compensation system 7, used for measuring the position 8 and the position of the chip on the reconstituted wafer to be exposed The relative position error of the pattern 9 to be exposed is calculated to obtain a correction model, and the lithography device is controlled to independently drive the mask table 3 drive module, the workpiece table 6 drive module or the objectiv...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More