Method for improving warping degree of silicon wafer and increasing alignment precision

A technology of overlay accuracy and warpage, which is applied in the data processing of the layout, improves the warpage of silicon wafers, and improves the overlay accuracy. Stress, effect of changing warpage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0055] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some of the embodiments of the present invention, not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

[0056] It should be noted that, in the case of no conflict, the embodiments of the present invention and the features in the embodiments can be combined with each other.

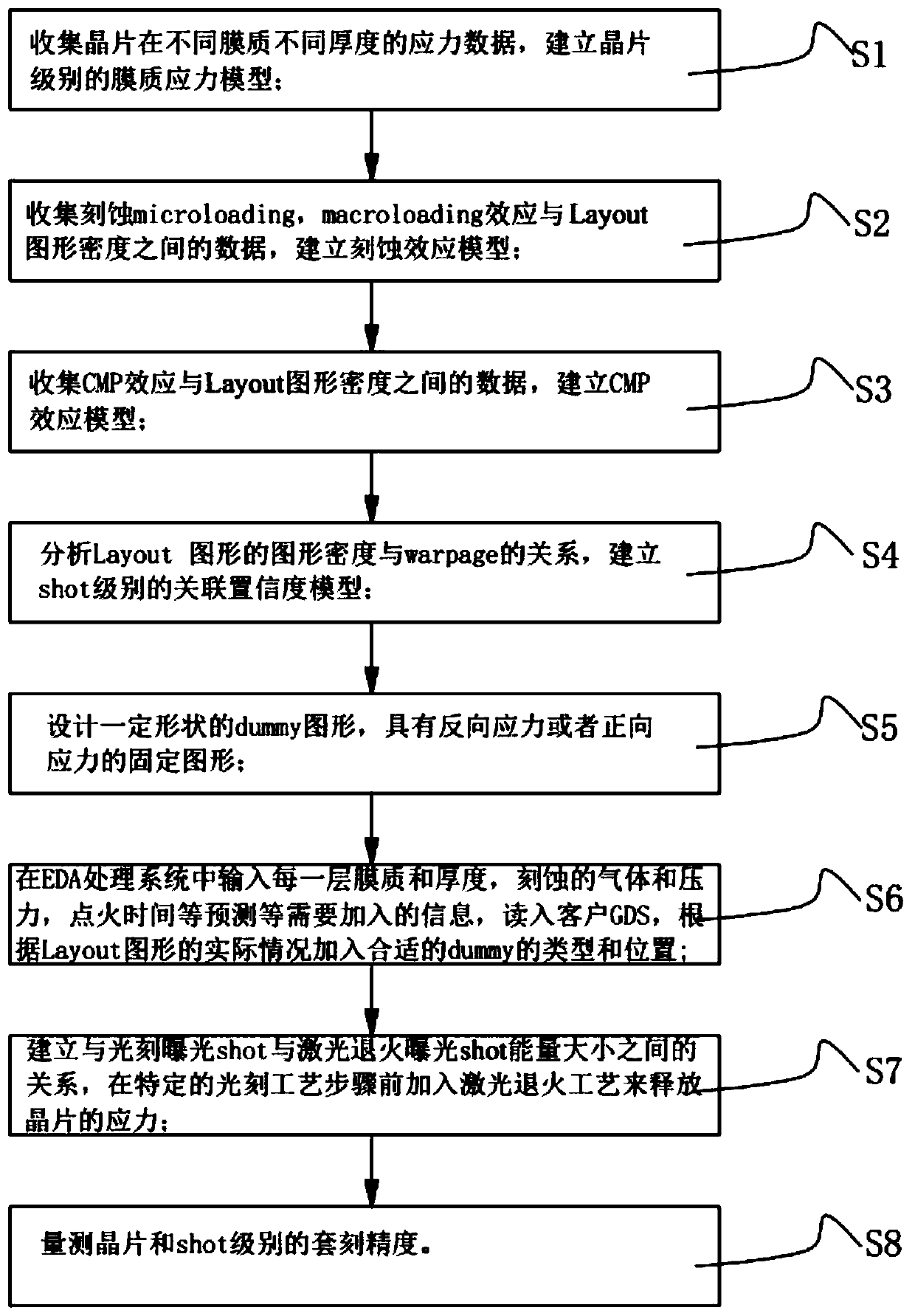

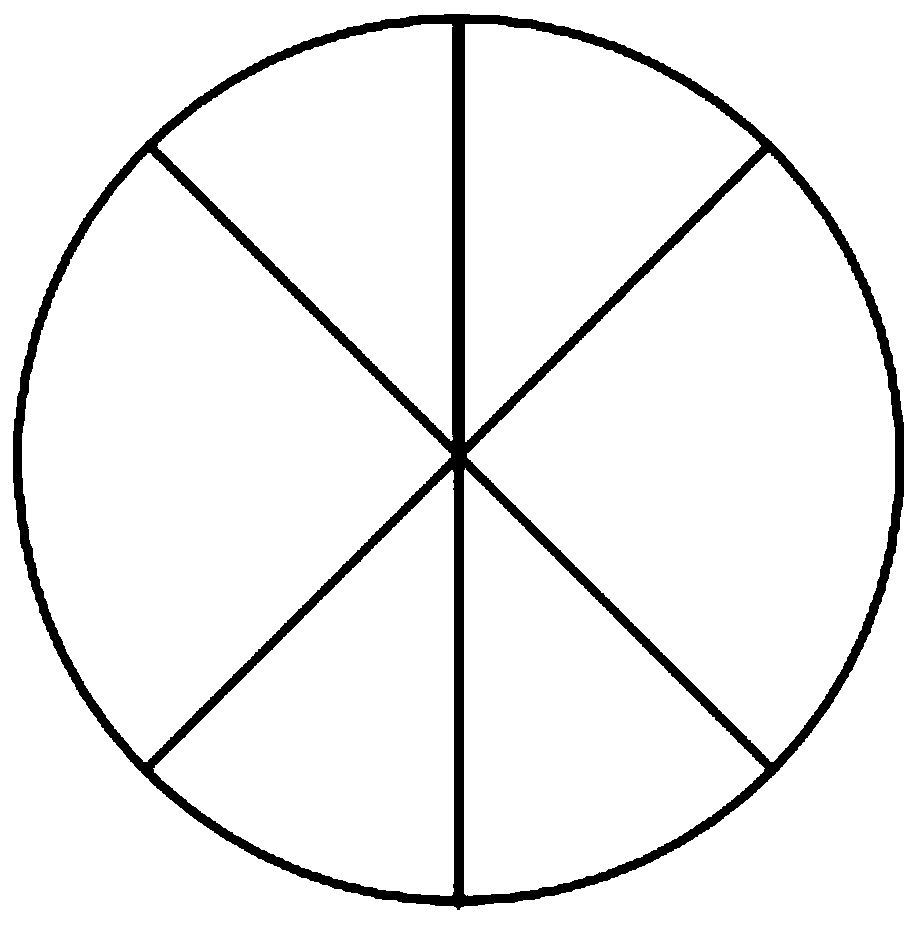

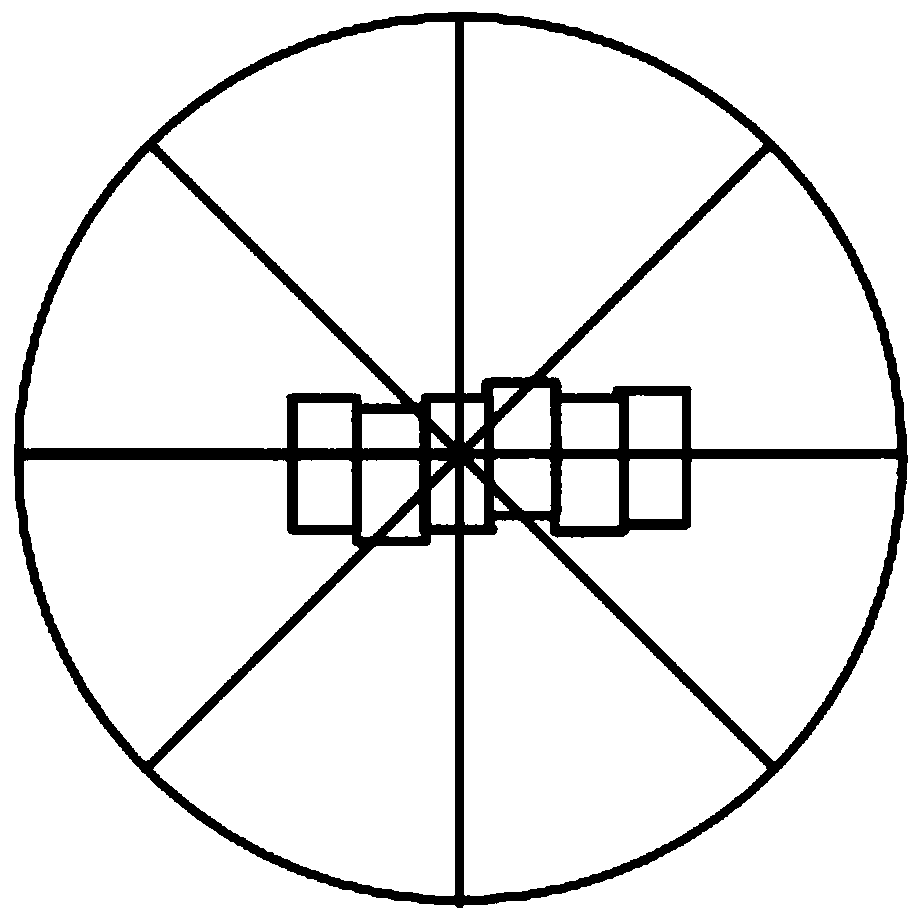

[0057] As a preferred embodiment, such as Figure 1-3 As shown, a method for improving the warpage of silicon wafers and improving the overlay accuracy, the film quality stress model used to obtain the stress data of silicon wafers, the relationship between the load effect of silico...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Overlap degree | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More