Preparation method of polysilicon layer, thin film transistor, array substrate and display device

A polysilicon thin film, polysilicon layer technology, applied in transistors, semiconductor devices, electric solid devices, etc., can solve the problems of poor grain uniformity, inability to effectively control the area, inability to effectively control the grain growth direction, etc., to achieve good performance, Good crystallization effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

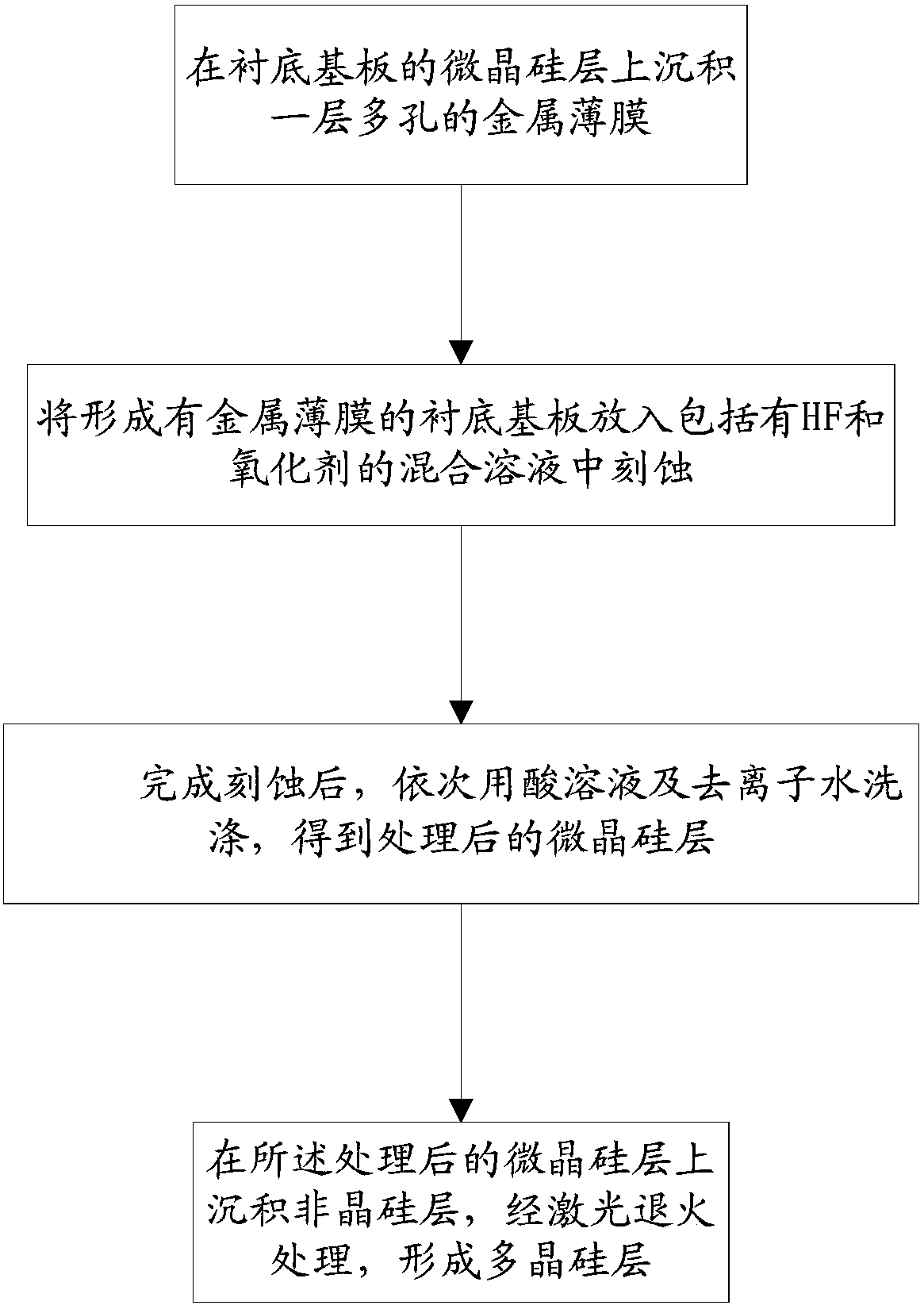

[0035] The embodiment of the present invention discloses a method for preparing a polysilicon layer, comprising the following steps:

[0036] Deposit a layer of porous metal thin film on the microcrystalline silicon layer of the base substrate;

[0037] Etching the base substrate on which the metal thin film is formed in a mixed solution including hydrogen fluoride and an oxidizing agent;

[0038] After the etching is completed, wash with acid solution and deionized water in sequence to obtain the treated microcrystalline silicon layer;

[0039] An amorphous silicon layer is deposited on the treated microcrystalline silicon layer, and a polycrystalline silicon layer is formed through laser annealing treatment.

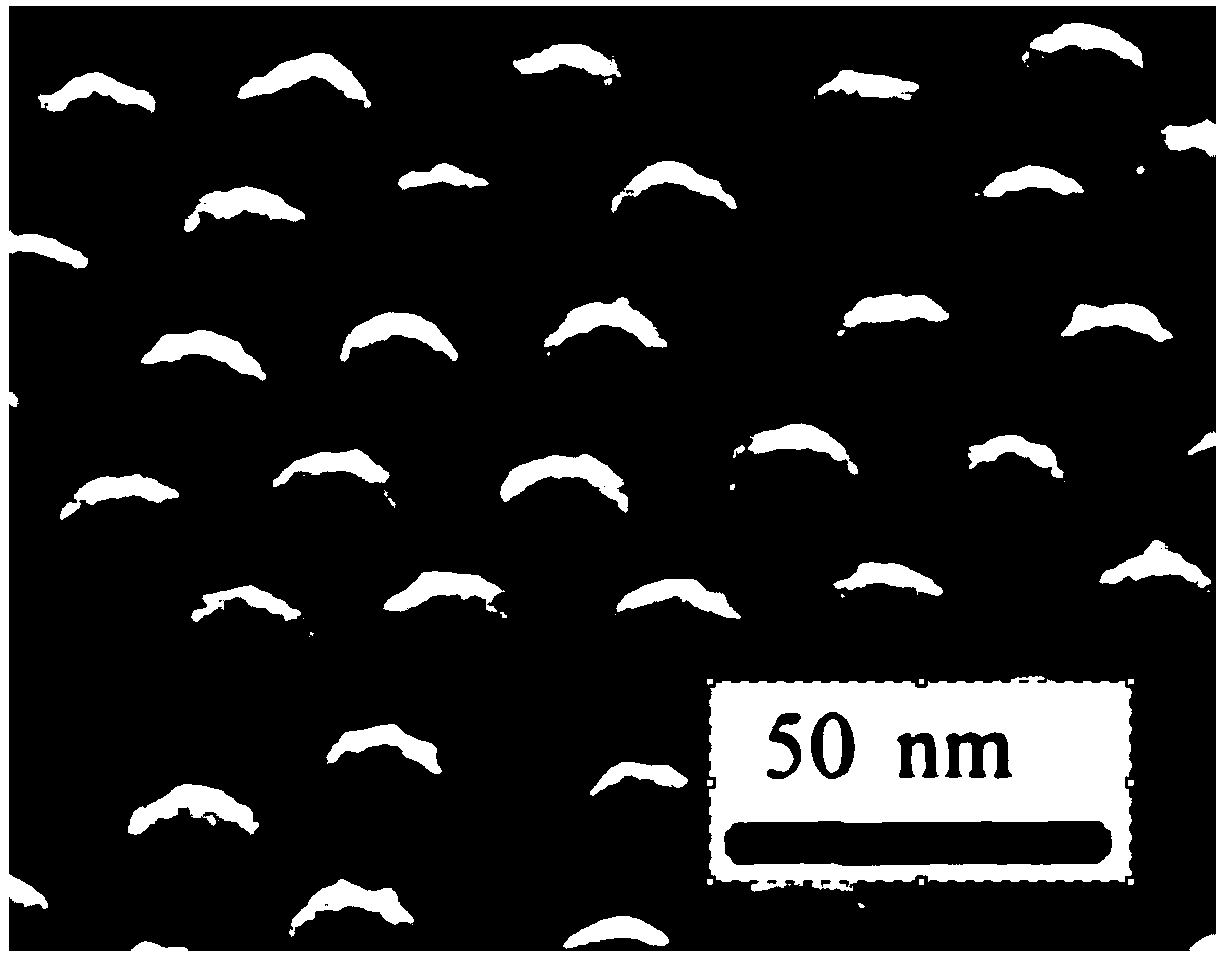

[0040] In the present invention, a porous metal film is deposited on the microcrystalline silicon layer, and the metal film is used to catalyze the etching of the microcrystalline silicon layer. The microcrystalline silicon in the metal-covered area is quickly corrode...

Embodiment 1

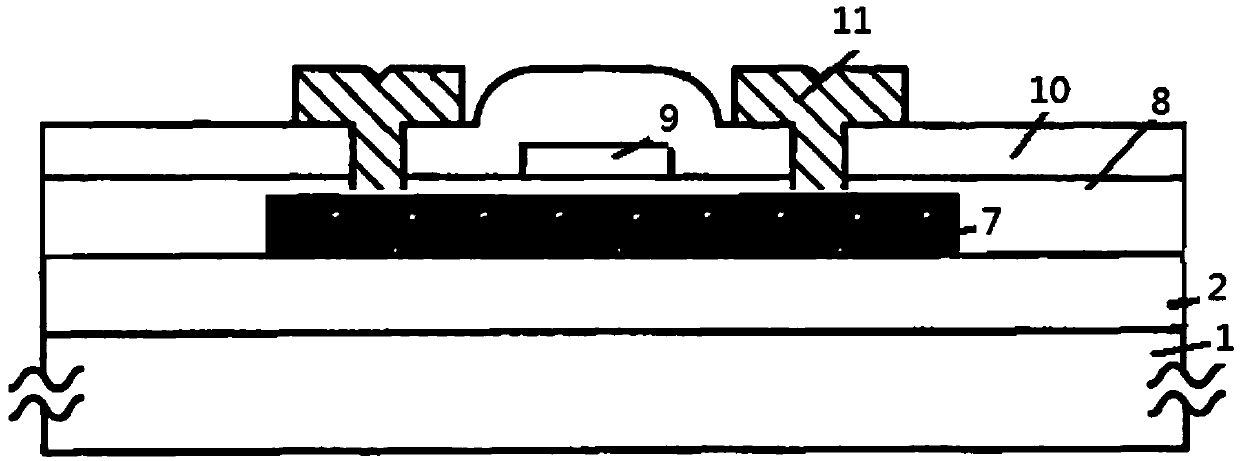

[0093] Deposit and form a SiN buffer layer with a thickness of 50-100 nm on the glass substrate.

[0094] A microcrystalline silicon layer with a thickness of 5-10 nm is deposited on the buffer layer.

[0095] The glass substrate after depositing the microcrystalline silicon layer was placed in hydrogen fluoride / AgNO 3 (the concentration of hydrogen fluoride is 3.0-5.0mol / L, the concentration of silver nitrate is 0.01-0.03mol / L) a porous Ag layer is deposited in the solution, and the time is about 60s;

[0096] At a reaction temperature of 50-80°C, the glass substrate is immersed in hydrogen fluoride / Fe(NO 3 ) 3 (the concentration of hydrogen fluoride is 0.2-0.5mol / L, the concentration of ferric nitrate is 8.0-12.0mol / L) and etch for 150-300s;

[0097] Take out the glass substrate, remove the Ag layer with HNO3 (the concentration of nitric acid is 4.0-6.0mol / L), wash it with a large amount of deionized water and then dry it; use PECVD equipment to deposit a 40-50nm amorphou...

Embodiment 2

[0103] Deposit and form a SiO buffer layer with a thickness of 150-300nm on the glass substrate.

[0104] A microcrystalline silicon layer with a thickness of 5-10 nm is deposited on the buffer layer.

[0105] The glass substrate after depositing the microcrystalline silicon layer was placed in hydrogen fluoride / AgNO 3 (the concentration of hydrogen fluoride is 3.0-5.0mol / L, the concentration of silver nitrate is 0.01-0.03mol / L) a porous Ag layer is deposited in the solution, and the time is about 60s;

[0106] At a reaction temperature of 50-80°C, immerse the glass substrate in hydrogen fluoride / H 2 o 2 (the concentration of hydrogen fluoride is 0.2-0.5mol / L, and the concentration of hydrogen peroxide is 0.04-0.08mol / L), etch for 150-300s;

[0107] Remove the glass substrate with HNO 3(The concentration of nitric acid is 4.0-6.0mol / L) to remove the Ag layer, wash it with a large amount of deionized water and dry it; use PECVD equipment to deposit a 40-50nm amorphous silic...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More