Combined method of dead zone elimination and dead zone compensation for three-level T-type inverter

A dead-zone compensation and inverter technology, applied to electrical components, AC power input conversion to DC power output, output power conversion devices, etc., can solve the problem of deteriorating inverter performance, increasing inverter voltage difference, etc. problem, achieve the effect of stable conversion process, reduce output voltage difference, and reduce modulation index

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] The specific implementation manners of the present invention will be described in detail below in conjunction with the accompanying drawings and examples.

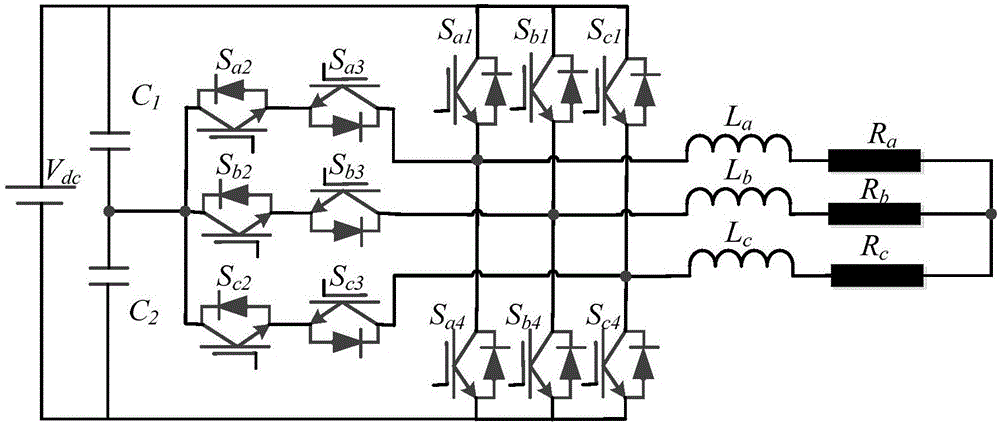

[0044] figure 1A three-level T-type inverter structure diagram is given, including three bridge arms in parallel, each phase bridge arm includes two series-connected IGBT switch tubes, and two IGBT switches in different directions are connected in series on one side of the midpoint of each phase bridge arm. The other side of the IGBT tube is connected to the load; the same DC voltage source is connected to each bridge arm end in parallel; the midpoint of the two midpoint clamping capacitors connected in parallel to the input voltage source is connected to the two directions of each phase bridge arm in different directions One end of the IGBT tube; each IGBT tube is driven by the control circuit.

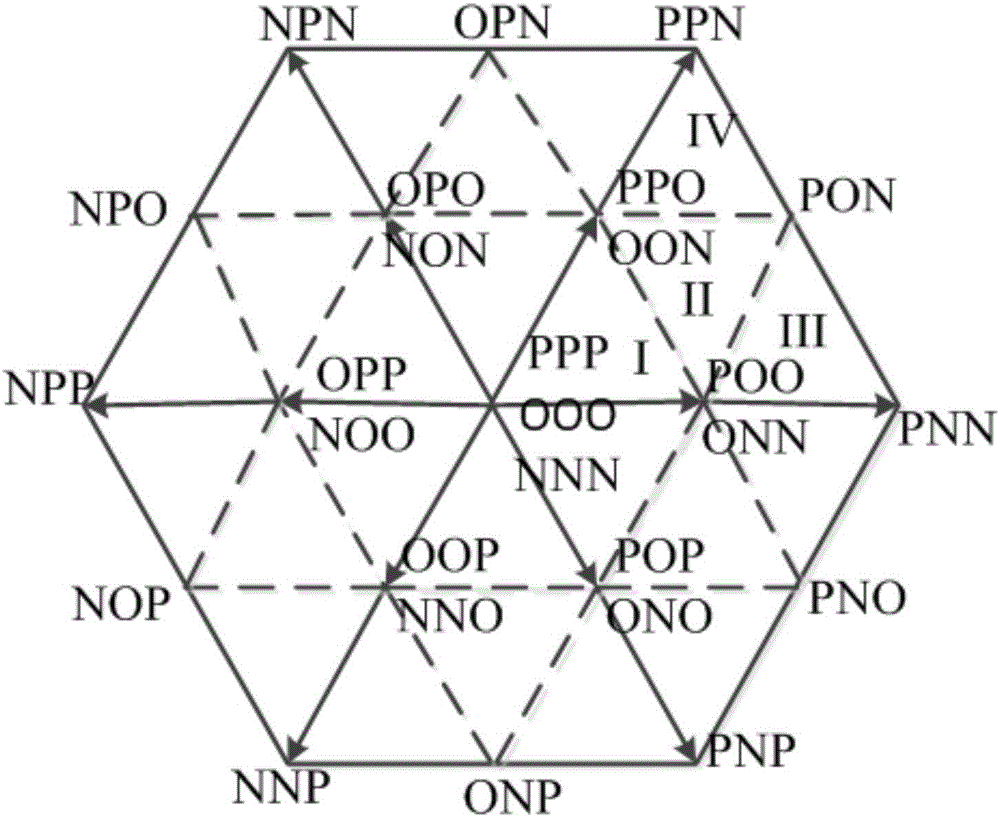

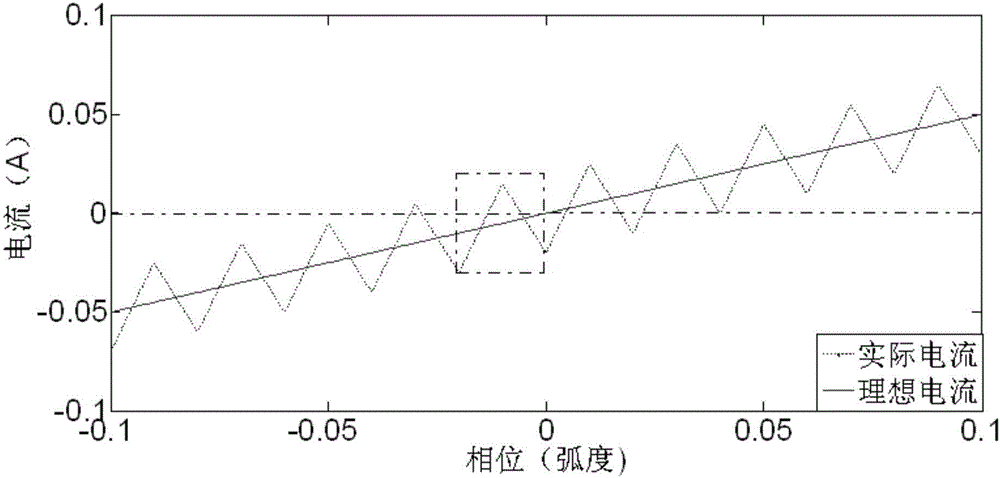

[0045] A combined method of dead zone elimination and dead zone compensation for a three-level T-type inverter, the met...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More