A circuit structure for realizing message selection from two

A circuit structure and message technology, applied in electrical components, digital transmission systems, data exchange networks, etc., can solve the problems of software that cannot be processed at line speed and low reliability, and achieve easy implementation, single function, and save control resources. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] Term explanation:

[0027] FPGA: Field-Programmable Gate Array, field programmable gate array;

[0028] ASIC: Application Specific Integrated Circuit, application specific integrated circuit;

[0029] DDR3 SDRAM: Double data rate type three SDRAM, DDR3 cache chip;

[0030] RAM: Random Access Memory, random access memory;

[0031] FIFO: First Fn First Out, first in first out storage unit.

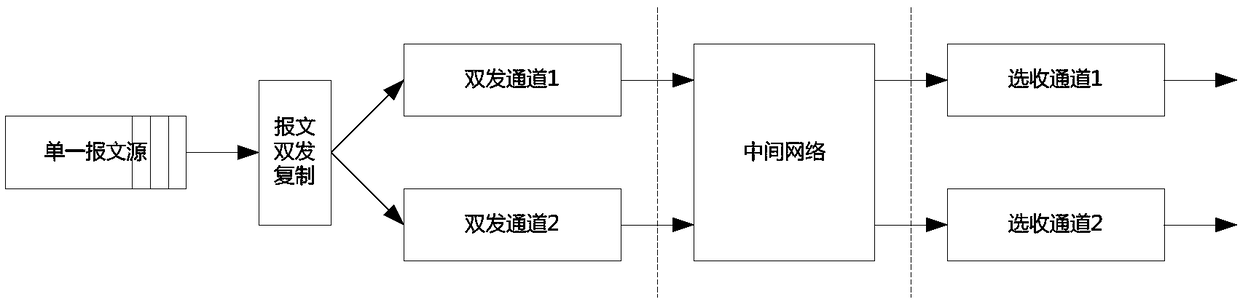

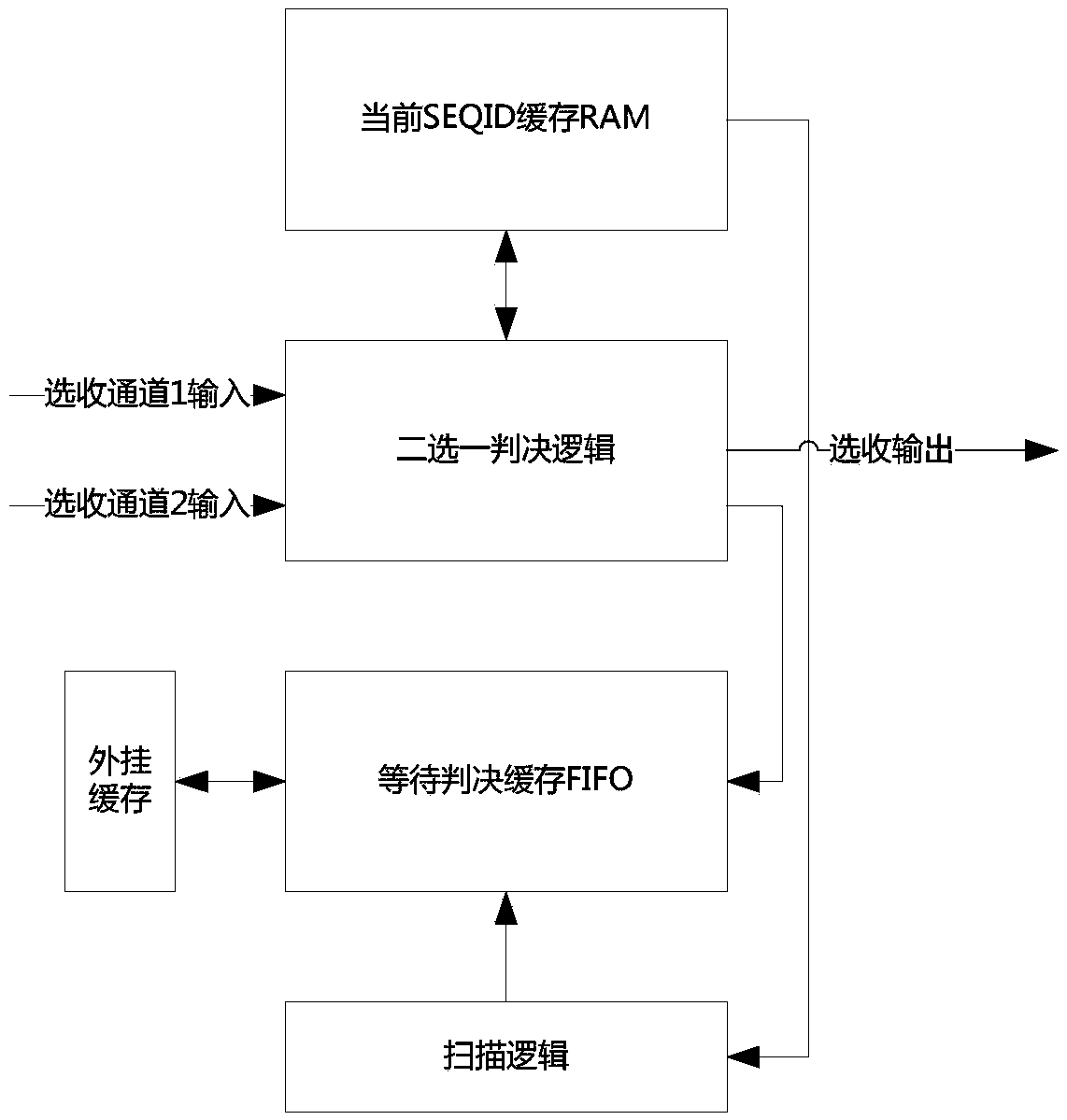

[0032] In order to realize the two-choice processing of the message, the message must carry the group number (GROUPID) and the stream number (SEQUENCEID, SEQID for short) information. The group number GROUPID refers to the number of message groups that undergo two-select-one processing, and the messages between different group numbers are independent of each other; the stream number SEQID refers to the sequence number of the message that is processed in the same group. The main condition of the logic of the two-choice decision.

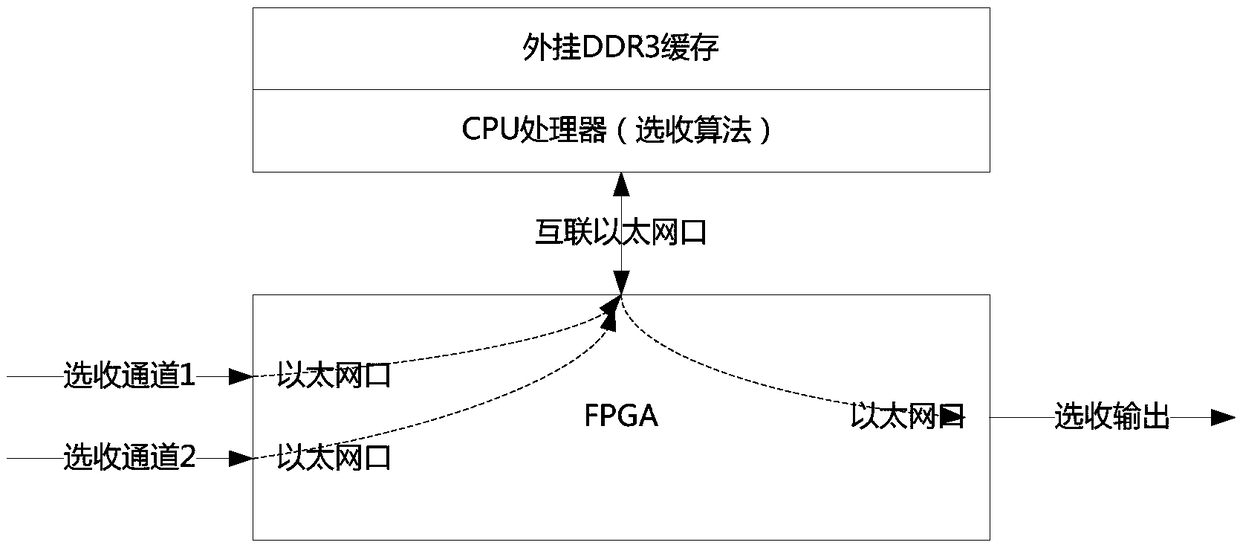

[0033] Such as Figure 2-3 As shown, a circuit structure for rea...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More