Rate-adaptive storer interface circuit

A memory interface and rate adaptive technology, applied in the field of interface circuits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The present invention will be further described below in conjunction with the accompanying drawings.

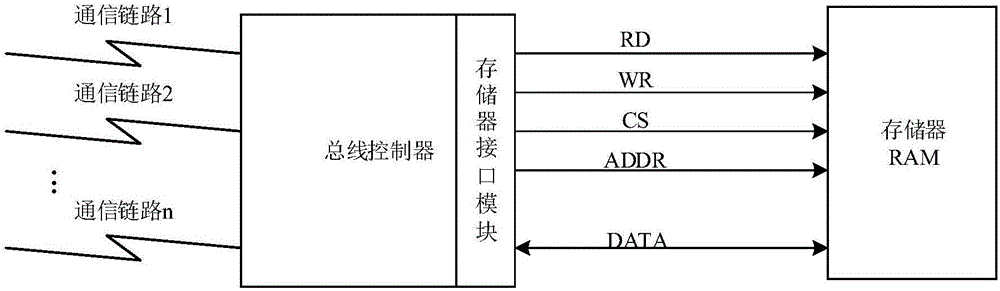

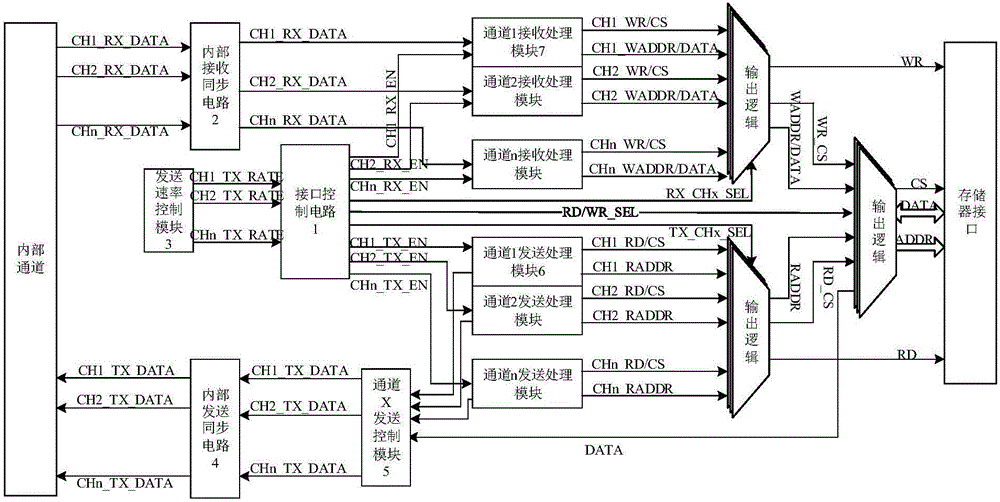

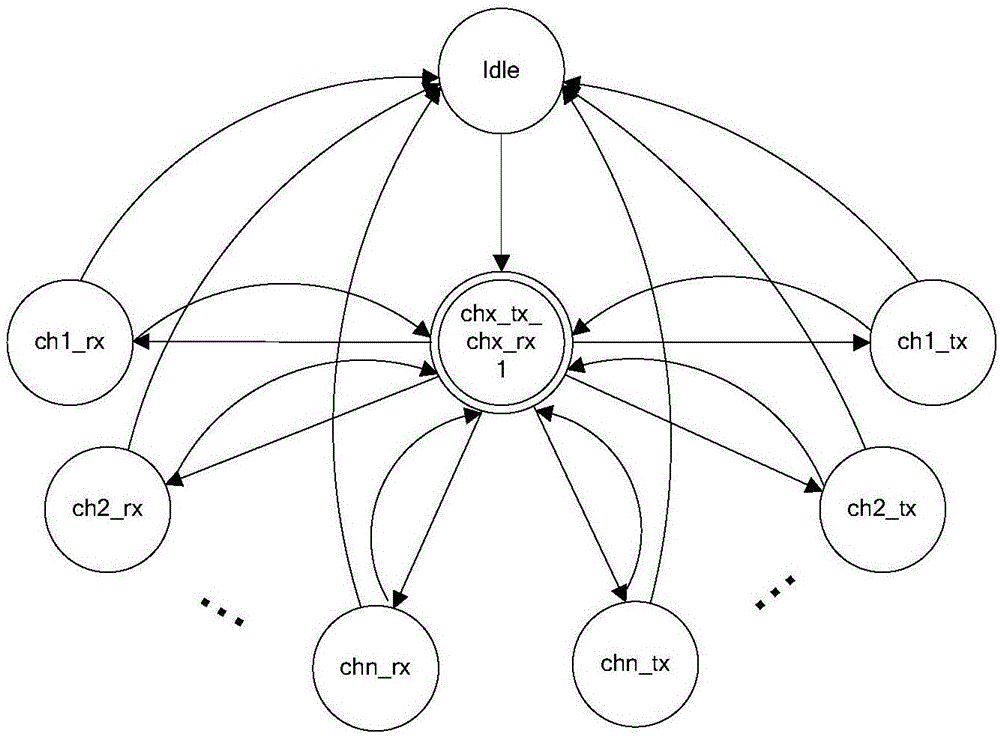

[0022] see figure 1 and figure 2 , the present invention includes an internal receiving synchronous circuit for receiving internal channel signals, and an interface control circuit for receiving and sending rate control module signals, the signals of the internal receiving synchronous circuit are sent to several receiving processing modules, and the signals of all receiving processing modules are sent to the first output A logic unit, the signal of the first output logic unit is sent to the memory interface through the third output logic unit; the signals of the several port control circuits are sent to several sending processing modules, and the signals of all sending processing modules are sent to the second output logic unit, The signal of the second output logic power supply is sent to the memory interface through the third output logic unit, and the output signa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More