A method for reducing the deformation of silicon wafer caused by adsorption of photolithography workpiece table

A technology of workpiece table and silicon wafer, which is applied in the field of photolithography technology, can solve the problems that cannot be directly eliminated, such as the difference of overlay precision vector, and achieve the effect of reducing overlay error, improving product yield and reducing error

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

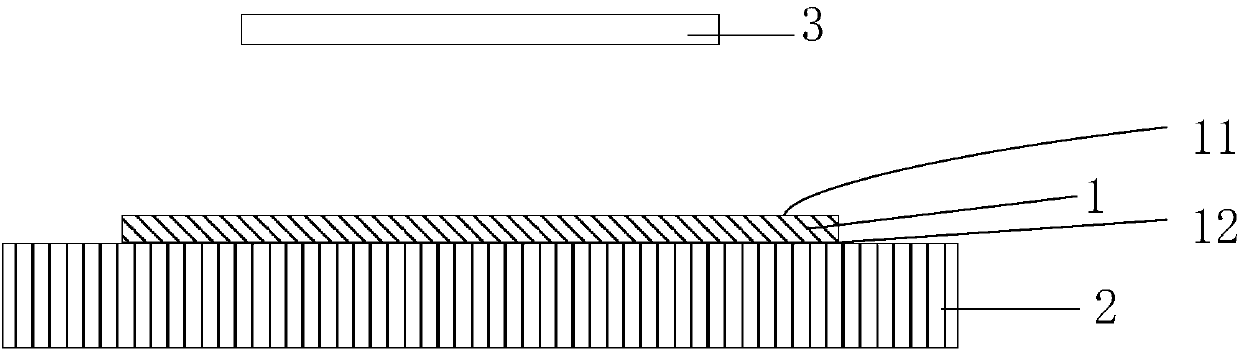

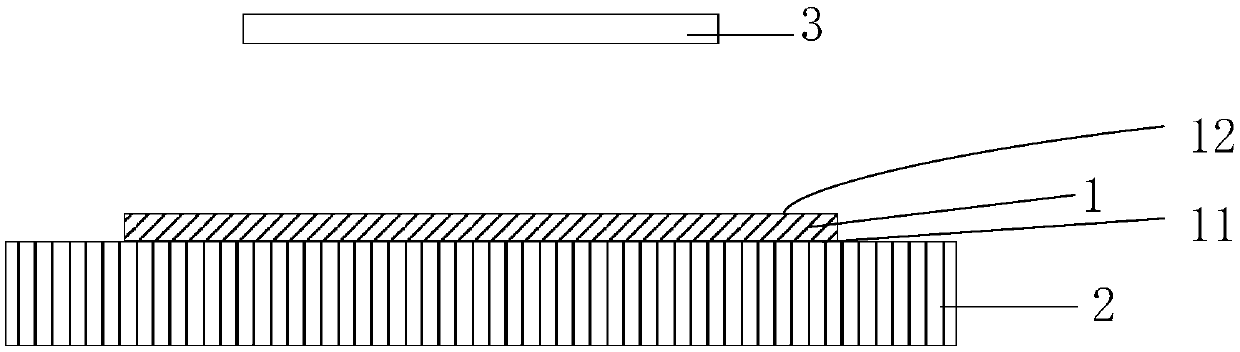

[0025] The specific embodiment of the present invention will be further described in detail below in conjunction with the accompanying drawings.

[0026] It should be noted that, in the following specific embodiments, when describing the embodiments of the present invention in detail, in order to clearly show the structure of the present invention for the convenience of description, the structures in the drawings are not drawn according to the general scale, and are drawn Partial magnification, deformation and simplification are included, therefore, it should be avoided to be interpreted as a limitation of the present invention.

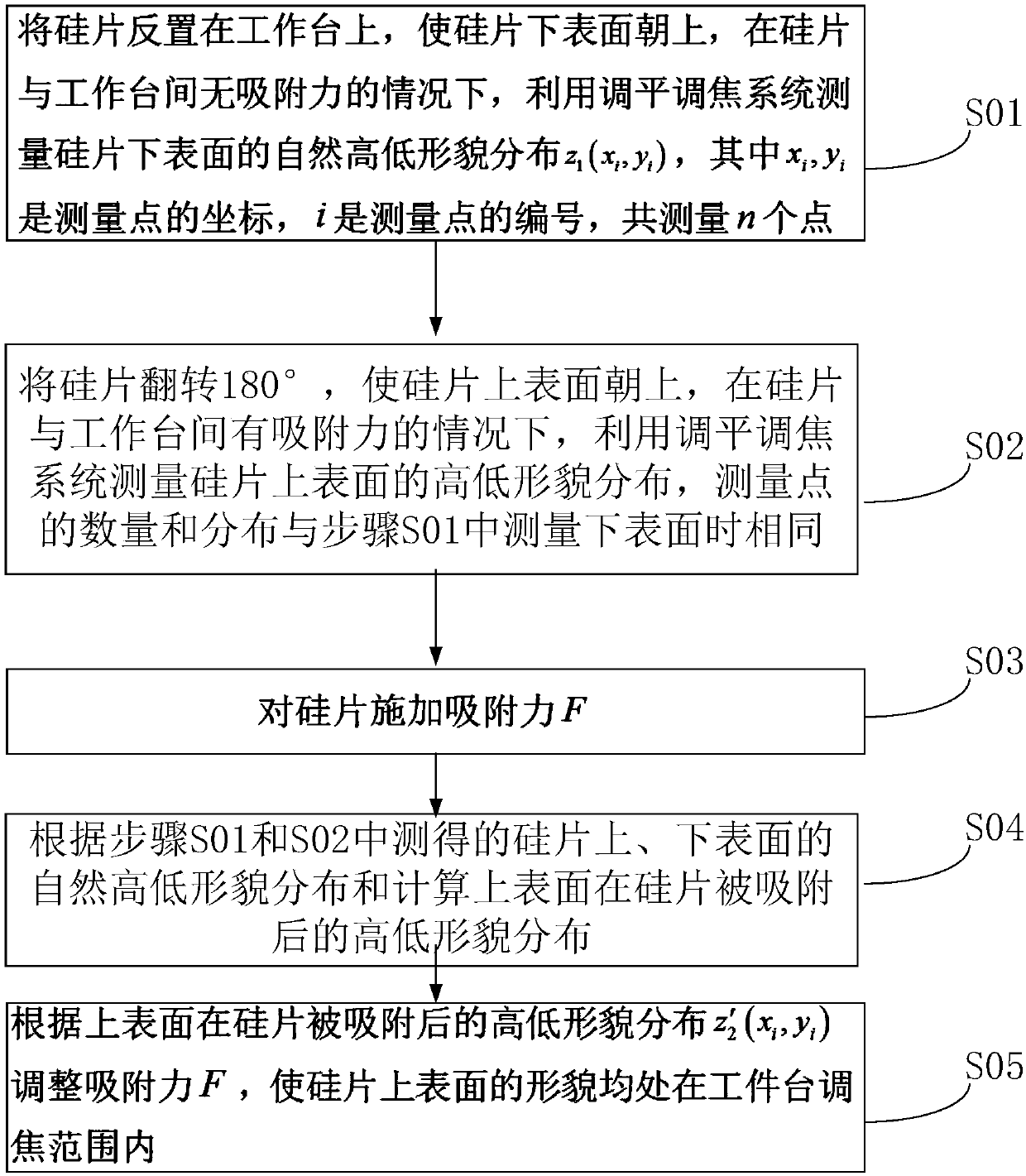

[0027] In the following specific embodiments of the present invention, please refer to figure 1 , figure 1 It is a schematic flow chart of a method for reducing the deformation of silicon wafers caused by the adsorption of photolithographic worktables in the present invention. Such as figure 1 As shown, a method disclosed in the present invention ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More