Implementation method of OpenPOWER CPU boot based on CPLD

An implementation method and a technology of a communication method, applied in the CPLD-based OpenPOWERCPUboot field, can solve problems such as unreliable communication, prolonging the boot time, and loss of returned results, so as to overcome the risks and hidden dangers of unreliable communication, shorten the boot time, and enhance stability sexual effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

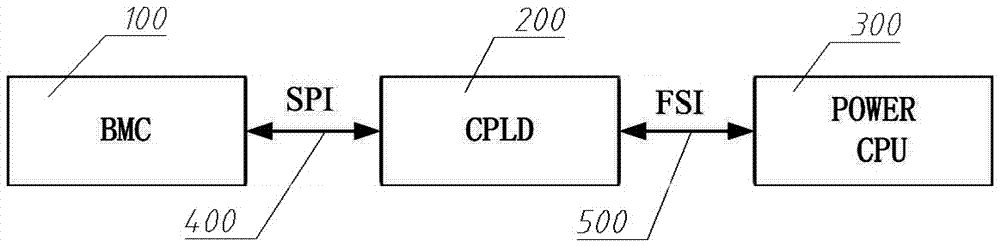

[0040] like figure 1 As shown, as the preferred best embodiment, it includes the following steps:

[0041] A method for realizing OpenPOWER CPU boot based on CPLD, in hardware design, CPLD 200 is set in the hardware connection between BMC 100 and POWERCPU 300, and communication connection is performed; BMC and CPLD can be connected through SPI bus, CPLD Realize the Master role function of the FSI protocol, and realize the protocol conversion function, and the POWER CPU acts as the FSISlave device. The BMC sends the boot command to the CPLD through the SPI bus. After the CPLD receives the command, it converts the command into the FSI protocol format and sends it to the POWER CPU. After the POWER CPU executes the command, it returns the result status to the CPLD through the FSI protocol. After CPLD receives the returned result, it converts it into SPI protocol and sends it to BMC. After the BMC receives the returned result, it can perform further processing according to the r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com