Two-stage splitting router applied to hierarchical network on chip and routing algorithm thereof

A router and routing technology, applied in the direction of data exchange network, digital transmission system, electrical components, etc., can solve the problem of increasing data packet delay, achieve the effect of increasing complexity and improving transmission efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0050] In this embodiment, the format of the data packet is as shown in Table 1. Each multicast data packet header microchip includes a virtual channel number flag, a microchip type flag, a data packet type flag, a destination node number, a source node number, a data packet current Transmission path, upper layer node number in the area where the destination node is located, upper layer network transmission direction;

[0051] Table 1 Network packet format

[0052]

[0053]

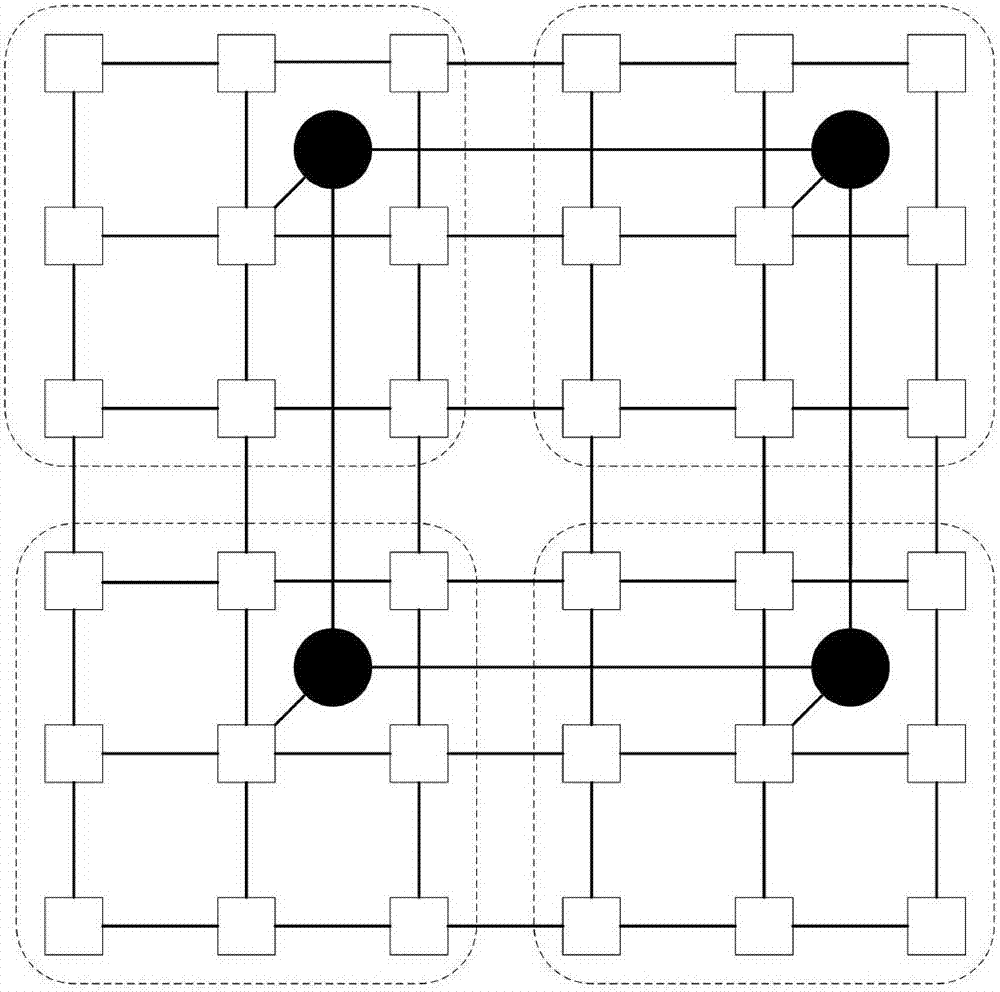

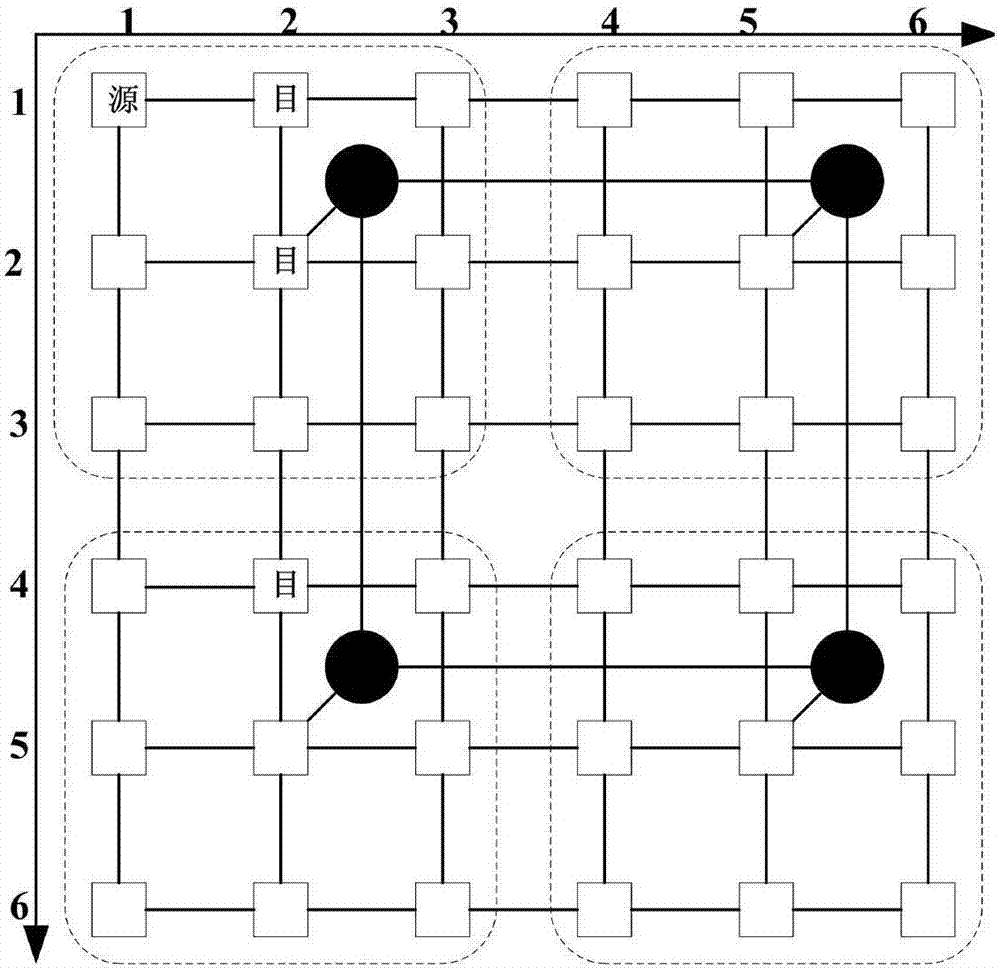

[0054] The hierarchical on-chip network structure adopted is a two-layer on-chip network composed of a 6×6 bottom-level two-dimensional network and a 2×2 upper-layer network, such as figure 1 As shown; the underlying two-dimensional network is divided into four areas; each area contains an intermediate router and several ordinary routers; ordinary routers include five transmission directions; intermediate routers include five transmission directions and one upward transmission direction; the upper l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More